Συγγραφή

Μηνάς Δασυγένης

Δημήτριος Σούντρης

Κριτικός Αναγνώστης

Γεώργιος Δημητρακόπουλος

Συντελεστές Έκδοσης

Τεχνική Επεξεργασία: Μηνάς Δασυγένης

Γραφιστική Επεξεργασία: Μηνάς Δασυγένης

ISBN: 978-960-603-390-2

Copyright ΣΕΑΒ, 2015

Το παρόν έργο αδειοδοτείται υπό τους όρους της άδειας Creative Commons Αναφορά Δημιουργού - Μη Εμπορική Χρήση - Όχι Παράγωγα Έργα 3.0. Για να δείτε ένα αντίγραφο της άδειας αυτής επισκεφτείτε τον ιστότοπο https://creativecommons.org/licenses/by-nc-nd/3.0/gr/

ΣΥΝΔΕΣΜΟΣ ΕΛΛΗΝΙΚΩΝ ΑΚΑΔΗΜΑΪΚΩΝ ΒΙΒΛΙΟΘΗΚΩΝ

Εθνικό Μετσόβιο Πολυτεχνείο

Ηρώων Πολυτεχνείου 9, 15780 Ζωγράφου

www.kallipos.gr

Το παρόν πόνημα γράφηκε για να χρησιμοποιηθεί ως βιβλίο θεωρίας για το μάθημα Ενσωματωμένα Συστήματα που διδάσκεται στο Τμήμα Μηχανικών Πληροφορικής και Τηλεπικοινωνιών του Πανεπιστημίου Δυτικής Μακεδονίας, από τον πρώτο συγγραφέα Μηνά Δασυγένη, και στη Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου, από τον δεύτερο συγγραφέα Δημήτριο Σούντρη. Μπορεί όμως, να χρησιμοποιηθεί ελεύθερα, είτε ολόκληρο, είτε τμηματικά, από οποιονδήποτε που ενδιαφέρεται να εκπαιδευτεί σε θέματα σχεδίασης Ενσωματωμένων Συστημάτων. Επειδή το βιβλίο αναφέρεται σε έναν τομέα που συνεχώς αλλάζει, θα πρέπει να υπάρχει κάποιος τρόπος ενημέρωσης των αναγνωστών. Για την καλύτερη οργάνωση και ενημέρωση, έχει δημιουργηθεί ένας ιστοχώρος υποστήριξης στη διεύθυνση http://arch.icte.uowm.gr/mdasyg/book/embedded, όπου θα τοποθετείται επιπρόσθετο υλικό, όπως παρουσιάσεις και ασκήσεις.

Επιπρόσθετα, ο πρώτος συγγραφέας έχει αναρτήσει στο κανάλι του (youtube) μια πλήρη σειρά μαγνητοσκοπημένων διαλέξεων για το μάθημα Ενσωματωμένα Συστήματα, στη διεύθυνση https://www.youtube.com/playlist?list=PLl2orJCvV3b4vwBe-6rJrcrcmQAVHoa3f, ενώ όλες οι σημειώσεις, οι παρουσιάσεις και οι εργαστηριακές ασκήσεις του μαθήματός του, είναι διαθέσιμες από το πρόγραμμα ανοικτών μαθημάτων Opencourses στη διεύθυνση http://arch.icte.uowm.gr/courses/embedded/. O ίδιος συγγραφέας έχει διαθέσει ελεύθερα το υλικό από όλα τα μαθήματα που διδάσκει, και για αυτό βραβεύτηκε από το Opencourses σε πλήθος 2500 ανοικτών μαθημάτων της Ανώτατης Εκπαίδευσης.

Η συγγραφή του παρόντος βιβλίου δεν θα ολοκληρωνόταν χωρίς τη συμπαράσταση μερικών ατόμων, που παρείχαν αμέριστη βοήθεια σε διάφορα στάδια της προσπάθειας. Αρχικά, θα ήθελα να ευχαριστήσω τον συν-συγγραφέα του βιβλίου Δημήτριο Σούντρη, που συνέβαλε τα μέγιστα για την άρτια, ποιοτική και ποσοτική, ολοκλήρωση του έργου με τις εξειδικευμένες γνώσεις του σε θέματα σχεδιασμού ενσωματωμένων συστημάτων, λόγω της συμμετοχής του σε ερευνητικά προγράμματα και των συνεργασιών με πανεπιστήμια και μεγάλες εταιρίες. Επίσης, θα ήθελα να ευχαριστήσω τον Γιώργο Δημητρακόπουλο, ο οποίος, ως κριτικός αναγνώστης, συνέβαλε στην ολοκλήρωση της συγγραφής με εύστοχες παρατηρήσεις και σχόλια.

Επιπλέον, θα ήθελα να ευχαριστώ τη Δράση «Ελληνικά Ακαδημαϊκά Ηλεκτρονικά Συγγράμματα και Βοηθήματα» (Ε.Α.Η.Σ.Β., η οποία υλοποιείται από τον Σ.Ε.Α.Β. και το Ε.Μ.Π.), που μου έδωσε τη δυνατότητα της ολοκλήρωσης και της έκδοσης του παρόντος βιβλίου.

Τέλος, περισσότερο από όλους θα ήθελα να ευχαριστήσω τον πατέρα μου Μιχάλη Δασυγένη, ο οποίος, ως ένας δεύτερος προσεκτικός αναγνώστης, με τροφοδοτούσε με σχόλια κατά τη διάρκεια της συγγραφής του βιβλίου, προκειμένου να ολοκληρωθεί με επιτυχία και εντός των αυστηρών χρονοδιαγραμμάτων η συγγραφή του.

Το παρόν πόνημα γράφηκε για να χρησιμοποιηθεί ως βιβλίο θεωρίας για το μάθημα Ενσωματωμένα Συστήματα που διδάσκεται στο Τμήμα Μηχανικών Πληροφορικής και Τηλεπικοινωνιών του Πανεπιστημίου Δυτικής Μακεδονίας, από τον πρώτο συγγραφέα Μηνά Δασυγένη, και στη Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου, από τον δεύτερο συγγραφέα Δημήτριο Σούντρη.

Το βιβλίο αυτό δύναται να χρησιμοποιηθεί σε συνδυασμό με το υποστηρικτικό υλικό, που βρίσκεται στη ιστοσελίδα του μαθήματος Ενσωματωμένα Συστήματα στη διεύθυνση http://arch.icte.uowm.gr/courses/embedded/ και με τις μαγνητοσκοπημένες διαλέξεις στο https://www.youtube.com/playlist?list=PLl2orJCvV3b4vwBe-6rJrcrcmQAVHoa3f.

Με το βιβλίο αυτό και με το υποστηρικτικό υλικό, επιτυγχάνονται τα παρακάτω μαθησιακά αποτελέσματα:

Στόχοι Θεωρίας: Οι φοιτητές κατανοούν:

τι είναι ενσωματωμένο σύστημα και τι ιδιαιτερότητες έχει,

τα δίκτυα επικοινωνίας στα ενσωματωμένα συστήματα,

πώς γίνεται ο συσχεδιασμός υλικού και λογισμικού,

τι είναι οι επιταχυντές υλικού και πότε χρησιμοποιούνται,

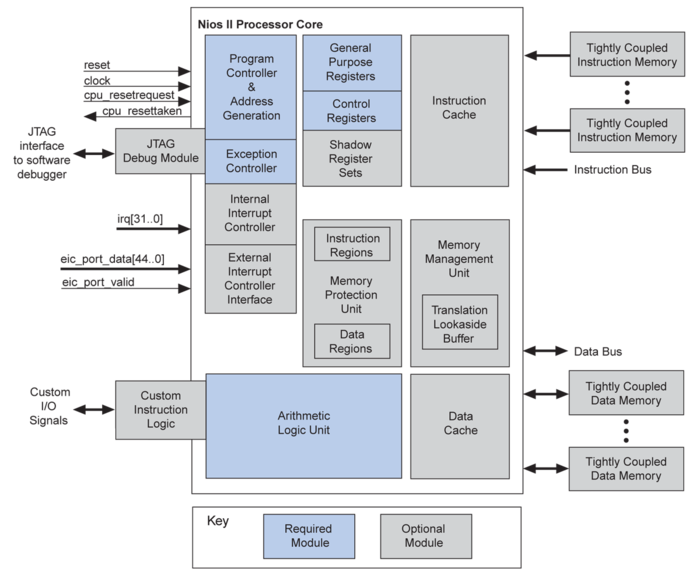

την αρχιτεκτονική δημοφιλών επεξεργαστών ενσωματωμένων συστημάτων,

τι είναι τα λειτουργικά συστήματα πραγματικού χρόνου,

τη σημασία των σκληρών και μαλακών περιορισμών,

την απόδοση των ενσωματωμένων συστημάτων.

Στόχοι Εργαστηρίου: Οι φοιτητές κατανοούν:

τον προγραμματισμό ενσωματωμένων συστημάτων, λαμβάνοντας υπόψιν τις ιδιαίτερες απαιτήσεις τους,

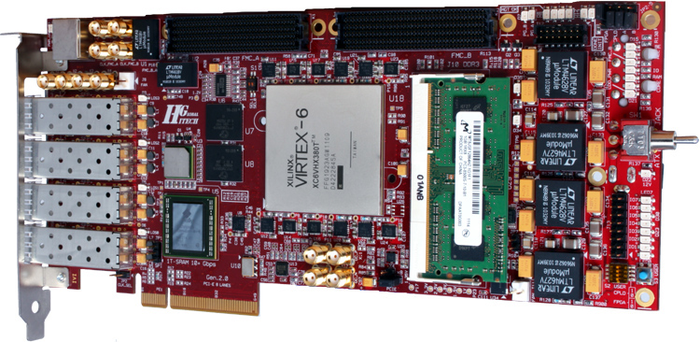

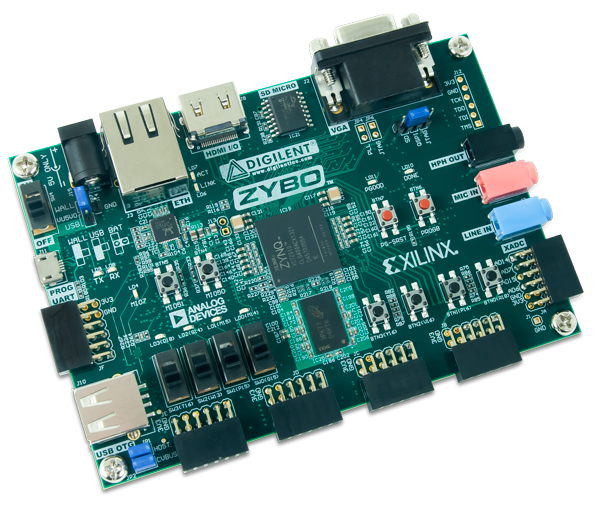

την ευελιξία των FPGA, ως ρεαλιστικών αρχιτεκτονικών υλοποίησης ενσωματωμένων συστημάτων.

Οι φοιτητές αποκτούν δεξιότητες στη(ν):

δημιουργία και βελτιστοποίηση προγραμμάτων ως προς τις επιδόσεις και την κατανάλωση ενέργειας,

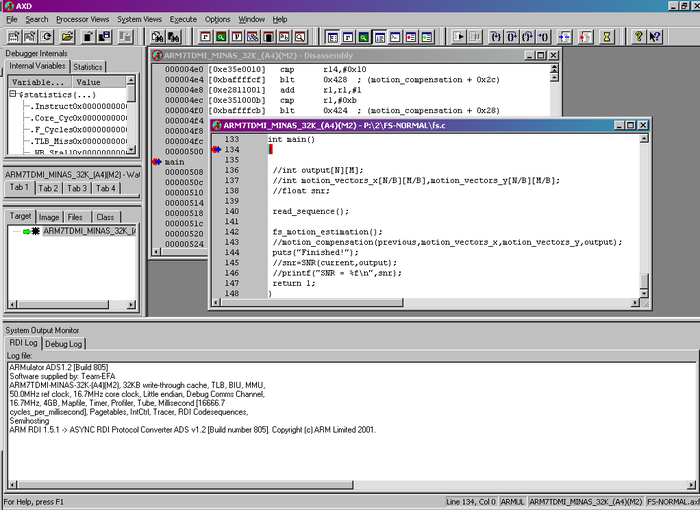

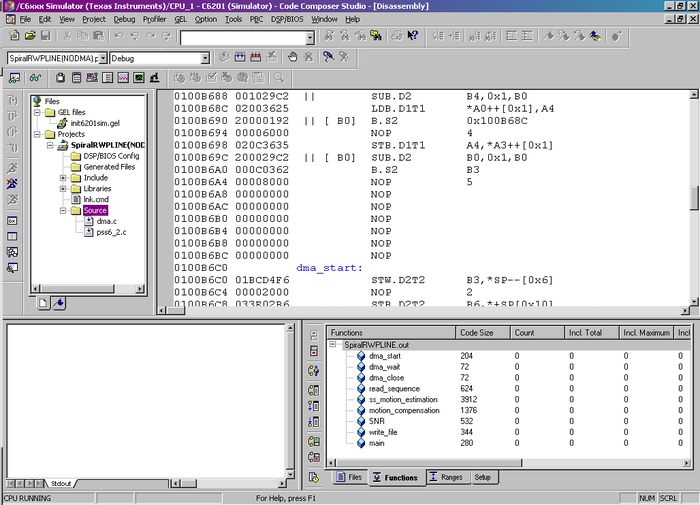

εξοικείωση με αναπτυξιακά περιβάλλοντα της ARM και της TI,

εκτενή χρήση της VHDL για περιγραφή μονάδων ενσωματωμένων συστημάτων,

χρήση των FPGA για εφαρμογές ενσωματωμένων συστημάτων,

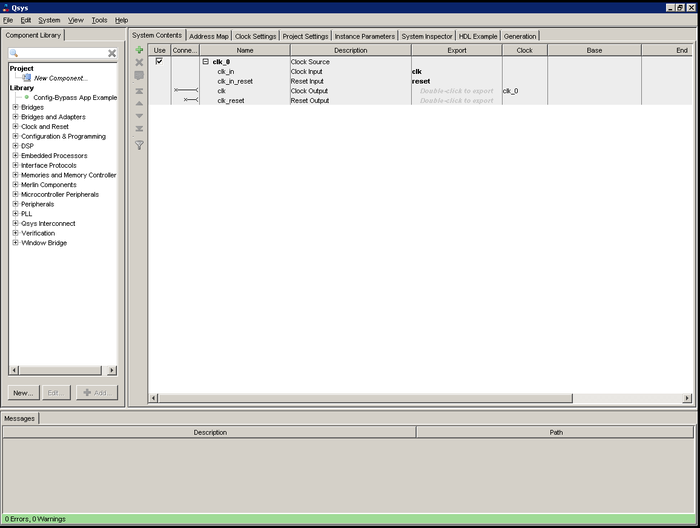

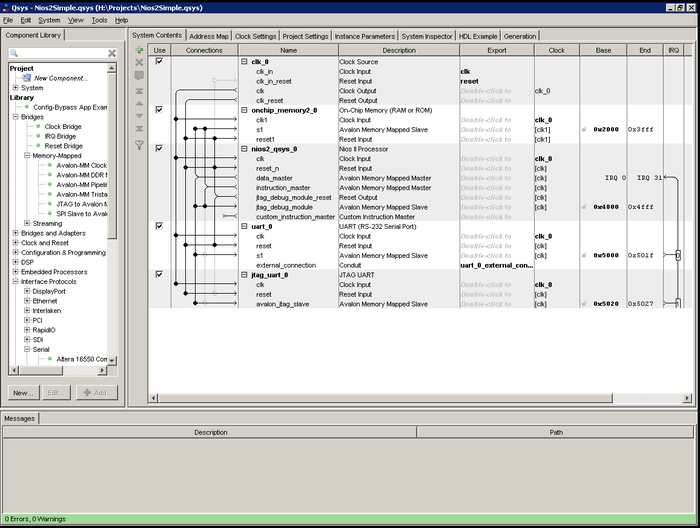

δημιουργία ενσωματωμένων συστημάτων με soft-cores,

δημιουργία ‘συστήματος σε ψηφίδα’ (System on Chip, SOC),

εφαρμογή της μεθοδολογίας DTSE, για βελτιστοποίηση εφαρμογών για ενσωματωμένα συστήματα,

δημιουργία και χρήση πυρήνων πνευματικής ιδιοκτησίας (IP cores),

σχεδίαση ενσωματωμένων συστημάτων λογισμικού σε C και υλικού σε VHDL.

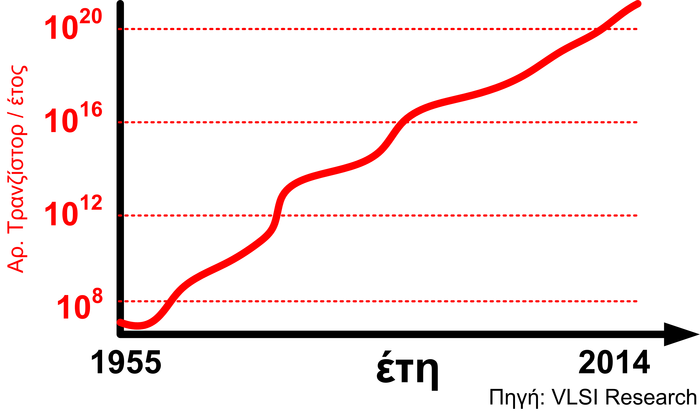

Τις τελευταίες δεκαετίες οι αναπτυγμένες κοινωνίες βιώνουν τα οφέλη της ψηφιακής εποχής. Η ανακάλυψη του τρανζίστορ το 1947 από τους John και Walter Brattain στα εργαστήρια της AT&T [1], αποτέλεσε το εφαλτήριο για μια επανάσταση δίχως προηγούμενο. Τα χρόνια που ακολούθησαν χαρακτηρίστηκαν από ανακαλύψεις, ευρεσιτεχνίες και πρωτοποριακές σχεδιάσεις και συσκευές που επηρέασαν κάθε τομέα της καθημερινότητας. Από το 1981 που άρχισε να πωλείται ο πρώτος προσωπικός υπολογιστής της IBM (IBM Personal Computer, PC), έως και τις μέρες μας που μπορούμε να προμηθευτούμε πολυπύρηνα συστήματα στο ίδιο υπόστρωμα του ολοκληρωμένου κυκλώματος, με ασύλληπτες επιδόσεις που χρησιμοποιούν τεχνολογίες υλοποίησης των 14 nm [2], τα τεχνολογικά προϊόντα δεν σταματάνε να μας εκπλήσσουν. Το πλήθος αυτών των προϊόντων φαίνεται και από τις πολλές κατηγορίες που καλύπτουν. Η πιο πολυπληθής και αφανής κατηγορία είναι αυτή των ενσωματωμένων συστημάτων. Σε αυτό το βιβλίο παρουσιάζουμε κάθε πτυχή του σχεδιασμού αυτών των συστημάτων, παρέχοντας όσο το δυνατόν πληρέστερη γνώση γύρω από το πολύ μεγάλο εύρος αυτών των συστημάτων που τα συναντάμε από τα ξυπνητήρια, έως και σε δορυφόρους.

Οι ψηφιακοί υπολογιστές που χρησιμοποιούμε είτε φανερά, είτε χωρίς να το γνωρίζουμε (όπως τα ενσωματωμένα συστήματα), έχουν παρουσιάσει μια μεγάλη εξέλιξη τις δεκαετίες από το 1940 και ύστερα. Πριν από το 1940 είχαν παρουσιαστεί κάποιες μηχανές που χρησιμοποιούσαν μηχανικά τμήματα (και άρα δεν ήταν ψηφιακοί), και είτε είχαν κατασκευαστεί, είτε είχαν παραμείνει στα σχηματικά διαγράμματα. Οι μηχανές αυτές βασίζονταν σε πολύπλοκες κατασκευές από μοχλούς, γρανάζια, ταινίες και διακόπτες και χρησιμοποιούνταν για τον υπολογισμό κάποιων βασικών σχέσεων με πράξεις της πρόσθεσης, της αφαίρεσης, του πολλαπλασιασμού και της διαίρεσης. Κάποια από αυτά τα μηχανήματα μπορούσαν να προγραμματιστούν με τη χρήση διάτρητων καρτών, δηλαδή καρτελών που είχαν σε συγκεκριμένα σημεία οπές προσδιορίζοντας μια αλληλουχία πράξεων, σαν ένα είδος σημερινού προγράμματος. Αυτός ο προγραμματισμός χρησιμοποιήθηκε κατά κύριο λόγο σε υφαντικές μηχανές. Οι πρώτες πρωταρχικές κατασκευές που χρησιμοποιούσαν το ψηφιακό σύστημα (δηλαδή, ένα σύστημα με δυο καταστάσεις, την ανοικτή και την κλειστή), άρχισαν να εμφανίζονται προς τα τέλη της δεκαετίας του 1930, και αυτό γιατί υπήρχε μια αδήριτη ανάγκη να βελτιωθεί η υπολογιστική ικανότητα.

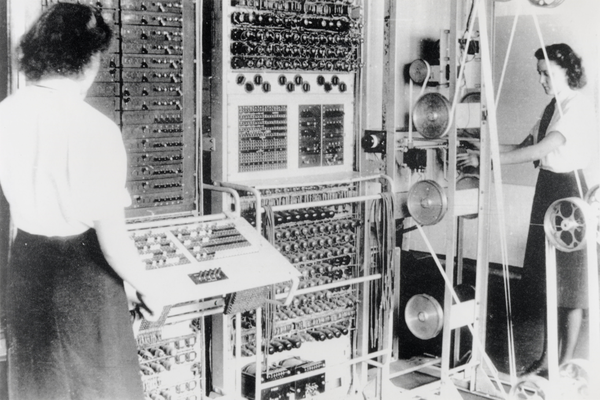

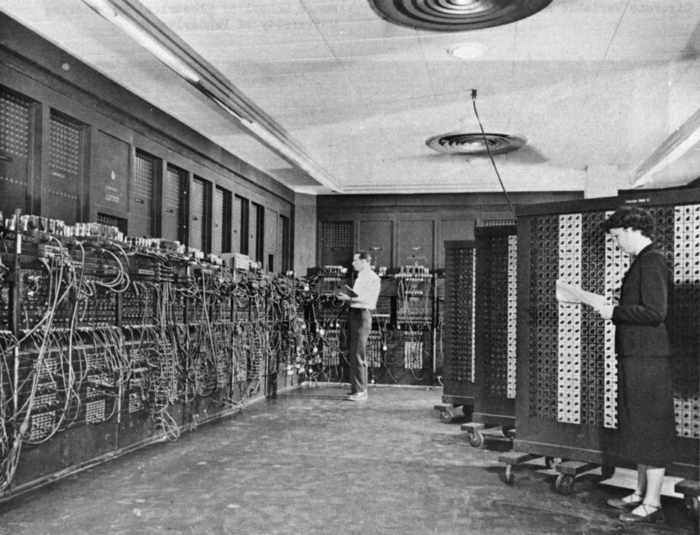

1.1: Η πρώτη ψηφιακή υπολογιστική μηχανή με το όνομα Colossus χρησιμοποιήθηκε με επιτυχία από τους συμμάχους για την αποκρυπτογράφηση των γερμανικών επικοινωνιών. Εικόνα από www.wikipedia.org.

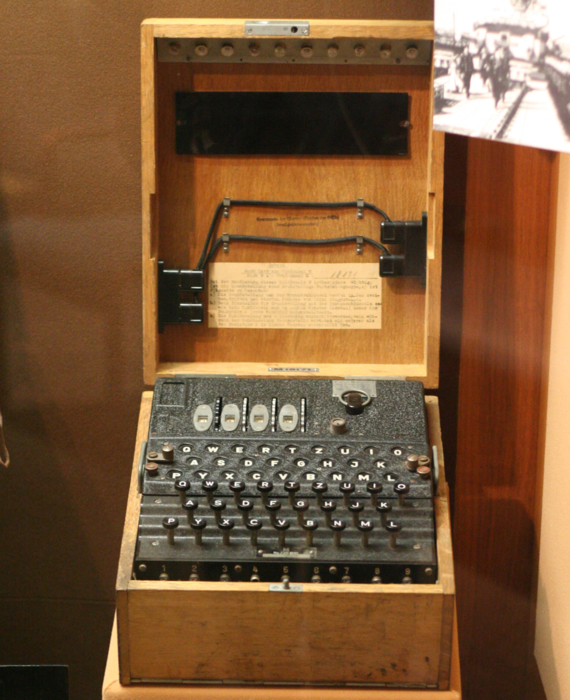

Η επιτακτική ανάγκη για τη βελτίωση της τεχνολογίας ήταν ο Β’ Παγκόσμιος Πόλεμος. Όπως ισχύει και στις μέρες μας, οι μεγαλύτερες τεχνολογικές ανακαλύψεις γίνονται για να καλυφθούν στρατιωτικές ανάγκες (ακόμη και το διαδίκτυο δημιουργήθηκε από τον Αμερικάνικο Στρατό προκειμένου να αυξήσουν την αξιοπιστία των επικοινωνιών σε περίπτωση πολέμου). Επιστήμονες, μηχανικοί και φυσικοί από όλες τις αντιμαχόμενες πλευρές, δημιούργησαν μεγάλες υπολογιστικές μηχανές για την κρυπτογράφηση και αποκρυπτογράφηση μηνυμάτων, υπολογισμό τροχιάς βλημάτων ή βελτίωση των επικοινωνιών. Η πρώτη υπολογιστική μηχανή που χρησιμοποιήθηκε με επιτυχία για να δώσει ένα προβάδισμα στους συμμάχους με την αποκρυπτογράφηση των γερμανικών επικοινωνιών, είναι το Colossus (Εικόνα 1.1) 1 που κατασκευάστηκε στην Αγγλία το 1943 από μια ομάδα, με επικεφαλείς τους Alan Turing και Tommy Flowers. Οι γερμανικές επικοινωνίες χρησιμοποιούσαν την κρυπτογράφηση με το μηχάνημα Enigma (Εικόνα 1.22) (το Enigma ήταν ένα μηχάνημα με γρανάζια που δε μπορούσε να επαναπρογραμματιστεί και για αυτό δεν θεωρείται υπολογιστής).

1.2: Το μηχάνημα Enigma που χρησιμοποιήθηκε για την κρυπτογράφηση/αποκρυπτογράφηση μηνυμάτων, χρησιμοποιούσε γρανάζια. Εικόνα από wikipedia.org.

Τα επόμενα χρόνια, στην άλλη πλευρά του Ατλαντικού Ωκεανού, κατασκευάστηκε ο υπολογιστής ENIAC (Electronic Numerical Integrator And Computer) (Εικόνα 1.33), προκειμένου να χρησιμοποιηθεί από τον Στρατό για τον υπολογισμό βαλλιστικών τροχιών (ήταν τα χρόνια του ψυχρού πολέμου που υπήρχε μεγάλη έρευνα για τα βαλλιστικά όπλα). Μάλιστα, επειδή ο Colossus αποτελούσε κρατικό μυστικό και ήταν απόρρητη η ύπαρξη του έως το 2000, πολλοί θεωρούσαν ότι ο ENIAC ήταν ο πρώτος προγραμματιζόμενος υπολογιστής (σε πολλά ακαδημαϊκά συγγράμματα αναφέρεται μόνο ο ENIAC). Επιπρόσθετα, ο ENIAC χρησιμοποιούσε το δεκαδικό σύστημα σε μια μορφή που είναι γνωστή ως BCD (binary coded decimal), ενώ ο Colossus χρησιμοποιούσε το δυαδικό σύστημα. Εκτός από αυτούς τους 2 υπολογιστές, παρουσιάστηκαν και άλλοι υπολογιστές, με υποδεέστερες, όμως, δυνατότητες (π.χ. δεν ήταν προγραμματιζόμενοι ή χρησιμοποιούσαν ηλεκτρικά ρελέ).

1.3: Ο πιο γνωστός υπολογιστής πριν το 1950 ήταν ο ENIAC. Εικόνα από wikipedia.org.

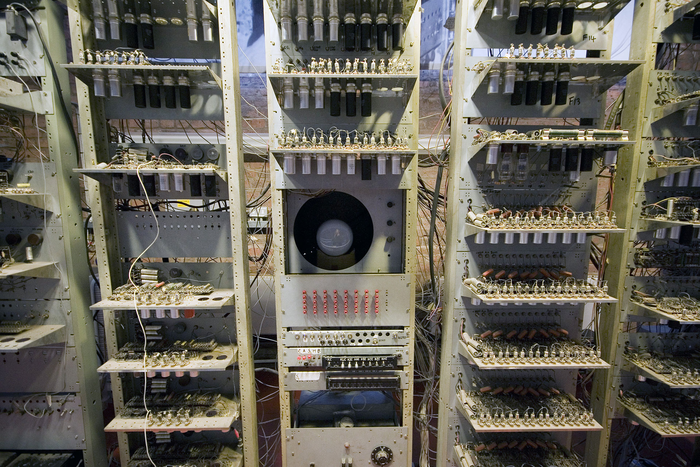

Η χρονιά, όμως, που σηματοδότησε τη μεγάλη επανάσταση στη βιομηχανία των ψηφιακών συστημάτων, είναι η χρονιά που ανακαλύφθηκε το τρανζίστορ (1947), το μικροσκοπικό αυτό στοιχείο που χρησιμοποιεί 3 ακροδέκτες, από τους οποίους ο ένας (η βάση) ρυθμίζει το ρεύμα (ως ροή ηλεκτρονίων) που διέρχεται διαμέσου των δυο άλλων επαφών, και έχει τη δυνατότητα να ανοίγει ή να κλείνει τη ροή των ηλεκτρονίων. Ο πρώτος υπολογιστής που χρησιμοποίησε τα τρανζίστορ ήταν ο Transistor Computer από το Πανεπιστήμιο του Manchester (Εικόνα 1.44). Τα επόμενα χρόνια παρουσιάστηκαν πλήθος υπολογιστών από Πανεπιστήμια όπως το MIT, Cambridge, Manchester κτλ ή από εταιρίες, όπως Intel, IBM, DEC, ARM, CRAY, κτλ., με πλήθος δυνατοτήτων και χαρακτηριστικών. Λόγω των διαφορετικών τεχνολογικών και φιλοσοφιών που χρησιμοποίησαν οι μηχανικοί και επιστήμονες για τη δημιουργία των υπολογιστών, έχει καθιερωθεί να τμηματοποιείται η εξέλιξη των υπολογιστών σε 5 γενιές.

1.4: Ο πρώτος υπολογιστής που χρησιμοποίησε transistor από το Πανεπιστήμιο του Manchester το 1953. Εικόνα από SSEM Manchester museum close up by Parrot of Doom - Own work. Licensed under CC BY-SA 3.0.

Η πρώτη γενιά των υπολογιστών χρησιμοποιεί λυχνίες κενού, και για αυτό το λόγο παρουσιάζει πολύ μικρό χρόνο ανάμεσα σε σφάλματα (MTBF, mean time between failures). Χρησιμοποιεί το δεκαδικό σύστημα (BCD), και δεν υπάρχει η δυνατότητα του εύκολου προγραμματισμού σε κάποια υψηλή γλώσσα. Το μέγεθος συνήθως είναι όσο ένα μεγάλο δωμάτιο ή αποθήκη, και η ταχύτητα επεξεργασίας είναι πολύ χαμηλή. Οι υπολογιστές αυτής της γενιάς μπορούν να χρησιμοποιήσουν καλώδια (patch cables), διακόπτες και περιστροφικά γρανάζια για τον προγραμματισμό. Οι πιο γνωστοί αντιπρόσωποι αυτής της κατηγορίας είναι ο Colossus και ο ENIAC. Ο ENIAC είχε βάρος 30 τόνους και καταλάμβανε 1300 τετραγωνικά μέτρα, ενώ η ταχύτητα του περιορίζονταν στις 500 προσθέσεις το δευτερόλεπτο.

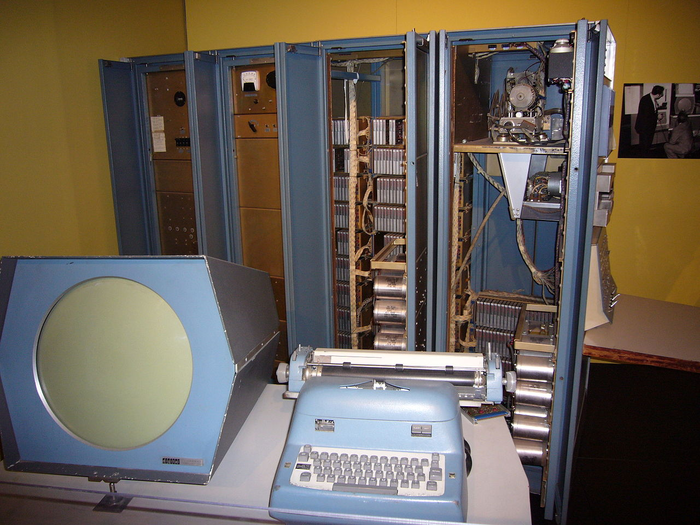

Η δεύτερη γενιά χρησιμοποιεί transistor, αλλά επειδή δεν έχουν σμικρυνθεί, είναι αρκετά ογκώδη μηχανήματα. Λόγω των τρανζίστορ, έχει βελτιωθεί αρκετά η αξιοπιστία τους, χρησιμοποιούν το δυαδικό σύστημα (αφού ταιριάζει με τις 2 καταστάσεις που έχουν τα τρανζίστορ - ανοιχτή και κλειστή), χρησιμοποιούν διάτρητες κάρτες, και εμφανίζονται και οι πρώτες γλώσσες προγραμματισμού. Το πιο γνωστό μηχάνημα αυτής της εποχής είναι ο PDP-1 της DEC (Εικόνα 1.55) που είχε μνήμη 4ΚB και συχνότητα λειτουργίας 0.2 Mhz, ενώ η αρχική του τιμή ήταν αρκετά υψηλή $100K USD. Το αξιοθαύμαστο ήταν η επεκτασιμότητα του συστήματος, αφού ο χρήστης μπορούσε να προμηθευτεί επιπρόσθετα, πληκτρολόγιο, εκτυπωτή, αποθηκευτικό χώρο, οθόνη και κάμερα.

1.5: Ο πρώτος εμπορικός υπολογιστής ήταν ο PDP-1 της DEC, που υποστήριζε πλήθος επιπρόσθετων περιφερειακών. Εικόνα από Matthew Hutchinson - http://www.flickr.com/photos/hiddenloop/307119987/. Licensed under CC BY 2.0 via Commons.

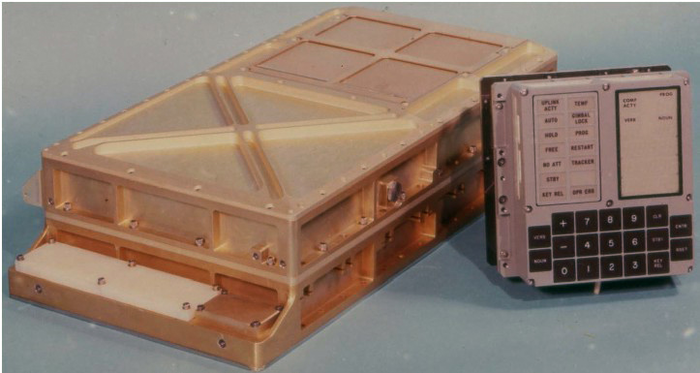

Η τρίτη γενιά έχει αυξημένη αξιοπιστία και χρησιμοποιεί λειτουργικά συστήματα που επιτρέπουν την ταυτόγχρονη εκτέλεση πολλαπλών προγραμμάτων (ψευδο-παράλληλα), αφού έχει χρονοδρομολογητή. Επιτρέπει την καλύτερη χρήση των υπολογιστικών πόρων (αφού πολλαπλοί χρήστες μοιράζονται τους πόρους ταυτόγχρονα) και χρησιμοποιεί ολοκληρωμένα κυκλώματα σε πυρίτιο, δηλαδή κυκλώματα με πολλά τρανζίστορ που κατασκευάζονται στην ίδια ψηφίδα πυριτίου με φωτολιθογραφικές μεθόδους. Στη γενιά αυτή χρησιμοποιείται και η έννοια της ιδεατής μνήμης, όπου επιτρέπει την καλύτερη εκμετάλλευση της ελάχιστης μνήμης RAM, με τη χρήση τεχνικών σελιδοποίησης και επέκτασης σε δευτερεύουσα μνήμη (σκληρό δίσκο). Το πιο αντιπροσωπευτικό παράδειγμα αυτής της κατηγορίας είναι το IBM System/360 που είχε 512KB RAM, με συχνότητα εκτέλεσης τα 4Mhz. O επεξεργαστής που χρησιμοποιούσε βασίζονταν σε καταχωρητές και είχε διασωλήνωση, ενώ χρησιμοποιούσε μικροκώδικα μέσα στους επεξεργαστές για να παρέχει συμβατότητα προς άλλα μηχανήματα. Αυτός ο υπολογιστής, που είχε μέγεθος όσο ένα μεγάλο διπλό ψυγείο, χρησιμοποιήθηκε σε μια πιο ‘ενσωματωμένη’ έκδοση (σε μέγεθος μιας βαλίτσας) για να εγκατασταθεί στο διαστημόπλοιο Apollo 11 που προσελήνωσε η NASA το 1969. Εμφανίστηκε, όμως, η ανάγκη για αύξηση της αξιοπιστίας του συστήματος και, έτσι, η IBM με 4000 μηχανικούς, σχεδίασε το ενσωματωμένο αυτό σύστημα, με μέσο χρόνο μεταξύ βλαβών στις 25000 ώρες και πυκνότητα ολοκλήρωσης 40000 στοιχείων ανά κυβικό πόδι (για τρισδιάστατη κατασκευή). Το Apollo Guidance Computer ήταν το πρώτο ενσωματωμένο σύστημα που κατασκευάστηκε (Εικόνα 1.76).

1.6: Ο πιο χαρακτηριστικός υπολογιστής της 3ης γενιάς ήταν ο IBM S/360. Εικόνα από τον Ben Franske της wikipedia.org - Licensed under CC BY 2.5 via Commons

Στη γενιά αυτή ανήκουν όλοι οι υπολογιστές από τα μέσα της δεκαετίας του 1990 και μετά. Οι υπολογιστές αυτοί έχουν πολύ μεγάλη αξιοπιστία, πολλές δυνατότητες, μεγάλη πυκνότητα ολοκλήρωσης, τα λειτουργικά συστήματα έχουν πλούσια και φιλικά περιβάλλοντα εργασίας, υποστηρίζουν πλήθος τεχνικών για την καλύτερη εκμετάλλευση των πόρων του συστήματος, όπως εικονική μνήμη, ψευδο-παραλληλισμός εργασιών, πολλαπλούς ταυτόχρονους χρήστες, πρωτόκολλα άμεσης πρόσβασης σε υλικό κτλ. Εκτός από το λογισμικό, το υλικό έχει επίσης βελτιωθεί, ενσωματώνοντας όλες τις βέλτιστες τεχνικές των τελευταίων 50 χρόνων, χρησιμοποιώντας πολύ μεγάλες πυκνότητες ολοκλήρωσης και νέους τρόπους επικοινωνίας και διασύνδεσης. Δεν υπάρχουν κάποια χαρακτηριστικά παραδείγματα αυτής της γενιάς, αφού ανήκουν όλοι οι υπολογιστές από το 2000 και μετά.

1.7: Το πρώτο ενσωματωμένο σύστημα που κατασκευάστηκε ήταν το Apollo Guidance Computer που τοποθετήθηκε στο ομώνυμο διαστημόπλοιο για το ταξίδι στη Σελήνη. Περιείχε μια μικρογραφία ενός IBM S/360. Εικόνα από commons.wikimedia.org - Public Domain.

Τα όρια ανάμεσα στην 4η και την 5η γενιά είναι δυσδιάκριτα. Για την ώρα δεν έχει εμφανιστεί αυτή η γενιά, και έτσι υπάρχουν μόνο προβλέψεις (με τον ίδιο κίνδυνο που υπάρχει σε κάθε πρόβλεψη, που είναι να μη γίνει με αυτόν τον τρόπο). Πάντως, η γενιά αυτή χαρακτηρίζεται από ακόμη πιο φιλικά λειτουργικά συστήματα, ενώ το υλικό θα έχει πολύ ωραία εμφάνιση και στυλ. Οι υπολογιστές αυτοί θα είναι ενσωματωμένοι γύρω μας (ubiquitous computing, πανταχόθεν υπολογιστική δυνατότητα) και δε θα μπορούμε να τους προσδιορίσουμε επακριβώς. Δύο χαρακτηριστικά, επομένως, είναι ότι οι υπολογιστές θα είναι αόρατοι και διασυνδεδεμένοι. Η επικοινωνία θα γίνεται με την ομιλία και όχι με πληκτρολόγιο ή ποντίκι. Δε θα υπάρχει το χάος των καλωδίων, αφού όλα θα είναι ασύρματα. Οι έξυπνες τηλεοράσεις θα είναι τόσο αναπτυγμένες, που δε θα χρειάζεται, όπως τώρα, η σύνδεση της έξυπνης τηλεόρασης με ένα mediaPC. Ο χρήστης θα έχει μια οθόνη για υπολογιστή, αλλά δε θα υπάρχει κεντρική μονάδα, αφού θα είναι ενσωματωμένη μέσα στην οθόνη. Τα αρχεία, τα προγράμματα και τα παιχνίδια θα βρίσκονται στο διαδίκτυο (‘σύννεφο’ – cloud) και θα είναι προσβάσιμα από οποιοδήποτε διασυνδεδεμένη συσκευή. Οι συσκευές του χρήστη θα είναι τερματικές συσκευές για απομακρυσμένη σύνδεση σε κεντρικούς διακομιστές του διαδικτύου. Η γενιά αυτή τώρα αρχίζει να εμφανίζεται και θα σχεδιαστεί από τη νέα γενιά μηχανικών, ίσως και από κάποιους από τους αναγνώστες αυτού του βιβλίου.

Οι περισσότεροι χρήστες μπορούν να αναγνωρίσουν ένα υπολογιστικό σύστημα, όπως ένα επιτραπέζιο υπολογιστή, ένα διακομιστή ή ένα φορητό υπολογιστή. Όμως, υπάρχει και ένας άλλος τύπος υπολογιστικών συστημάτων που είναι αθέατος για αυτούς που δε το γνωρίζουν και είναι ο κόσμος των ενσωματωμένων συστημάτων. Ο κόσμος αυτός είναι πολύ μεγαλύτερος από τον κόσμο των τυπικών υπολογιστικών συστημάτων, αφού κατασκευάζονται ετησίως δισεκατομμύρια μονάδες ενσωματωμένων συστημάτων σε σύγκριση με τις τυπικές υπολογιστικές μονάδες που κυμαίνονται σε κάποια εκατομμύρια Έχει υπολογισθεί ότι σε ένα τυπικό σύγχρονο σπίτι υπάρχουν 1-2 υπολογιστές και πάνω από 50 ενσωματωμένα συστήματα. Τι είναι όμως τα Ενσωματωμένα Συστήματα (ΕΣ);

Ένας πρώτος ορισμός για τα ΕΣ, είναι ότι σε αυτά κατηγοριοποιείται οποιαδήποτε συσκευή η οποία περιλαμβάνει έναν προγραμματιζόμενο επεξεργαστή, ο οποίος δεν είναι ένας επεξεργαστής γενικού σκοπού. Βέβαια, υπάρχουν και άλλοι ορισμοί και περισσότερες λεπτομέρειες για το πως ορίζεται ένα ΕΣ, αλλά αυτές θα αναλυθούν στη συνέχεια.

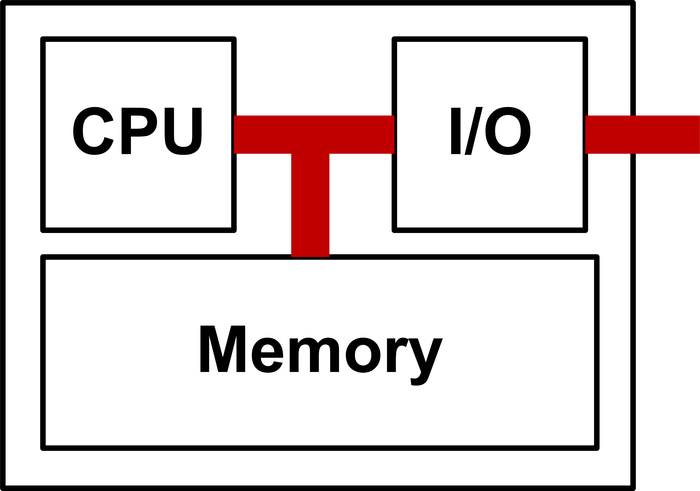

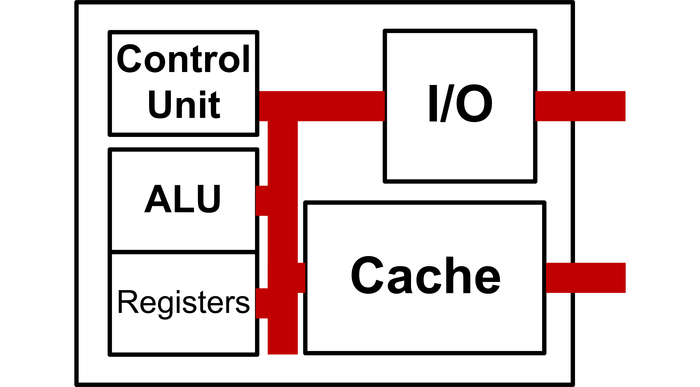

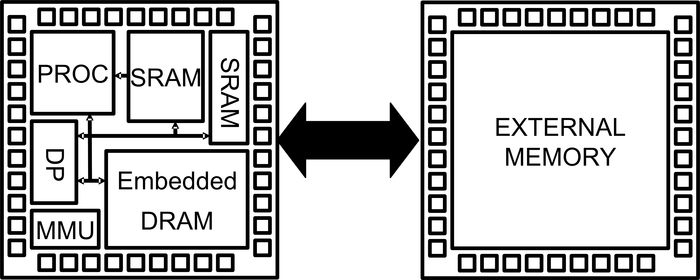

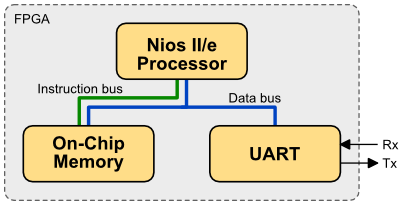

Τα ενσωματωμένα συστήματα έχουν ίδια αρχιτεκτονική με τα τυπικά υπολογιστικά συστήματα. Όπως κάθε προγραμματιζόμενο ψηφιακό σύστημα, έτσι και αυτά έχουν έναν ή περισσότερους επεξεργαστές, μια μνήμη και διεπαφές εισόδου εξόδου 1.8. Τα διαφορετικά στοιχεία των ενσωματωμένων συστημάτων είναι ότι χρησιμοποιούν άλλες κατηγορίες επεξεργαστών (συνήθως με χαμηλές δυνατότητες για αυτό και ονομάζονται και μικροεπεξεργαστές), με περισσότερες δυνατότητες διασύνδεσης εισόδου/εξόδου και πολύ λιγότερους πόρους (π.χ. μνήμη). Ένα ενσωματωμένο σύστημα, μπορεί να θεωρηθεί ως μια μικρογραφία ενός τυπικού υπολογιστικού συστήματος. Οι διαφορετικές απαιτήσεις των ΕΣ, έχουν οδηγήσει στη διαφοροποίηση από τα τυπικά υπολογιστικά συστήματα, όπως θα συζητηθεί στις επόμενες ενότητες.

1.8: Ένα ΕΣ έχει, όπως και τα τυπικά υπολογιστικά συστήματα, έναν επεξεργαστή, μία μνήμη και τουλάχιστον έναν τρόπο επικοινωνίας με το περιβάλλον (είσοδο/έξοδο).

Κατά την τελευταία δεκαετία, τα ενσωματωμένα συστήματα, παρόλο που, αρχικά, είχαν εμφανιστεί ως συσκευές, ή προϊόντα χαμηλών επιδόσεων (όπως ρολόγια και ηλεκτρονικοί υπολογιστές τσέπης), σήμερα χρησιμοποιούνται σε αρκετά πολύπλοκες συσκευές με αυξημένες απαιτήσεις σε επιδόσεις, όπως π.χ. είναι τα φορητά τερματικά πολυμέσων, ή οι ψηφιακοί προσωπικοί βοηθοί. Έτσι, τα ενσωματωμένα συστήματα έχουν γίνει πλέον μέρος της καθημερινής ζωής των περισσότερων ανθρώπων (στις τεχνολογικά αναπτυγμένες κοινωνίες) και, μάλιστα, μερικές φορές τα χρησιμοποιούν χωρίς καν να το γνωρίζουν. Γι’ αυτό το λόγο, αρκετοί ερευνητές έχουν χαρακτηρίσει τα ενσωματωμένα συστήματα ως επανάσταση των ηλεκτρονικών συσκευών.

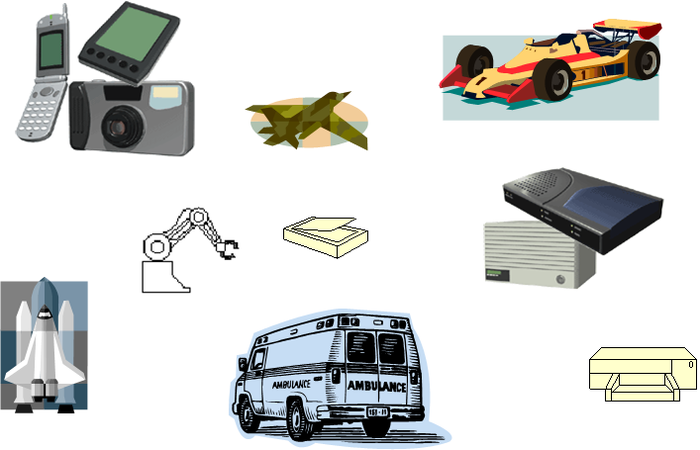

1.9: Τα ενσωματωμένα συστήματα βρίσκονται σχεδόν παντού.

Τα ενσωματωμένα συστήματα τα συναντάμε παντού. Αν και οι περισσότεροι από εμάς γνωρίζουμε ότι καθημερινά κατασκευάζονται εκατομμύρια υπολογιστές σε όλον τον κόσμο, αυτό που ίσως δεν ξέρουμε είναι ότι κατασκευάζονται πολλά περισσότερα (δισεκατομμύρια) ενσωματωμένα συστήματα για ένα πλήθος διαφορετικών λειτουργιών. Αυτό οφείλεται στο γεγονός ότι τα ενσωματωμένα συστήματα δεν τα βλέπουμε αφού είναι ‘ενσωματωμένα’ στις ψηφιακές συσκευές. Έχει υπολογιστεί ότι στις τεχνολογικά αναπτυγμένες κοινωνίες, αν και μόνον ένα ποσοστό 40% διαθέτει προσωπικό υπολογιστή, κάθε σπίτι έχει τουλάχιστον 30 ενσωματωμένα συστήματα.

Το Σχήμα 1.9 δείχνει κάποια τυπικά παραδείγματα από την καθημερινή μας ζωή στα οποία υπάρχουν ενσωματωμένα συστήματα. Συνήθως τα ενσωματωμένα συστήματα, σε αντίθεση με τους υπολογιστές γενικού σκοπού, χρησιμοποιούνται για εξειδικευμένες εφαρμογές και έχουν περιορισμένη χρήση. Ένας γενικός ορισμός θα μπορούσε να είναι ότι ενσωματωμένο σύστημα είναι κάθε ψηφιακό σύστημα που εκτελεί κάποια λειτουργία και δεν είναι προσωπικός υπολογιστής, φορητός υπολογιστής ή κεντρικός διακομιστής (mainframe). Η καλύτερη κατανόηση, όμως, του τι είναι ενσωματωμένο σύστημα, θα γίνει με την παρουσίαση κάποιων παραδειγμάτων. Μερικά παραδείγματα ενσωματωμένων συστημάτων είναι:

Τηλεοράσεις και βίντεο. Οι τηλεοράσεις έχουν ενσωματωμένους επεξεργαστές για να ελέγχουν την εικόνα, να ρυθμίζουν τα κανάλια, να εκτυπώνουν μηνύματα πάνω στην εικόνα, να απενεργοποιούν και να ενεργοποιούν τα κυκλώματα της τηλεόρασης.

Συσκευές τηλε-ελέγχου. Οι συσκευές τηλε-ελέγχου (telecontrol) έχουν ενσωματωμένους επεξεργαστές για να μετατρέπουν τις εντολές του χρήστη σε σήματα υπερύθρων για να ελέγχουν άλλες συσκευές.

Κινητά/Ασύρματα τηλέφωνα. Τα κινητά τηλέφωνα έχουν ενσωματωμένους επεξεργαστές για να διεκπεραιώνουν τις διαδικασίες αποκωδικοποίησης/κωδικοποίησης της φωνής, για να υλοποιούν το πρωτόκολλο επικοινωνίας και να εκτελούν τις πολύπλοκες εφαρμογές του τηλεφώνου.

Οχήματα. Όλα τα σύγχρονα αυτοκίνητα έχουν ένα πλήθος από ενσωματωμένους επεξεργαστές, είτε για την προστασία των επιβατών, είτε για βοηθητικές ενδείξεις, είτε για τη βελτίωση των συνθηκών οδήγησης.

Συσκευές νοικοκυριού. Οι σύγχρονες συσκευές νοικοκυριού (φούρνοι, πλυντήρια, ψυγεία κ.α.) έχουν ενσωματωμένους επεξεργαστές, για να προστατεύουν τα τρόφιμα ή τα ρούχα από λανθασμένες ρυθμίσεις, για να βελτιώνουν τις διαδικασίες συντήρησης ή μαγειρέματος και γενικά να αποτελούν τους βοηθούς της νοικοκυράς.

Αυτόματοι πωλητές. Οι αυτόματοι πωλητές έχουν ενσωματωμένους επεξεργαστές για να διεκπεραιώνουν τη λειτουργία της πώλησης αγαθών.

Εκτυπωτές/Φαξ. Οι συσκευές αυτές έχουν ενσωματωμένα συστήματα για τον έλεγχο της εκτύπωσης, της μετατροπής των δεδομένων σε εντολές προς τους μηχανισμούς εκτύπωσης, και της διασύνδεσης με άλλα συστήματα.

Φωτογραφικές μηχανές/Μηχανές βιντεολήψης. Και αυτές οι συσκευές έχουν ένα η παραπάνω ενσωματωμένα συστήματα για να ρυθμίζουν αυτόματα κάποια χαρακτηριστικά, ή να αποθηκεύουν με βέλτιστο τρόπο τα δεδομένα που λαμβάνουν.

Ένας λόγος που εξηγεί γιατί τα ενσωματωμένα συστήματα είναι τόσο δημοφιλή, είναι το ότι αποτελούνται από υλικό υψηλών επιδόσεων σε συνδυασμό με ένα εξειδικευμένο λογισμικό, ένας συνδυασμός που έχει πολύ μικρό χρόνο σχεδιασμού και εισόδου στην αγορά (short time to market).

Τα παραδείγματα της προηγούμενης ενότητας αποτελούν λίγα από τα πραγματικά υπαρκτά ενσωματωμένα συστημάτα. Είναι σαφές ότι υπάρχει μια δυσκολία στη διατύπωση ενός ορισμού που θα κάλυπτε όλες αυτές τις περιπτώσεις. Το πλήθος των ορισμών για τα ενσωματωμένα συστήματα είναι ίσως ανάλογο του αριθμού των σχεδιαστών που ασχολούνται με αυτά. Η λέξη ενσωματωμένο υποδηλώνει ότι το σύστημα είναι ‘ενσωματωμένο’ σε μια άλλη συσκευή και ότι η λειτουργία του δε θα τροποποιηθεί από τη στιγμή που θα γίνει διαθέσιμο στην αγορά. Αν και αυτός ο ορισμός φαίνεται σωστός, εντούτοις υπάρχουν κάποιες περιπτώσεις που προκαλούν σύγχυση. Για παράδειγμα, ένας προσωπικός υπολογιστής που εκτελεί μόνο ένα πρόγραμμα (π.χ. κιόσκι πολυμέσων) είναι ενσωματωμένο σύστημα; Ή ένας σύγχρονος προσωπικός ψηφιακός βοηθός που μπορεί να εκτελέσει ένα πλήθος προγραμμάτων αντίστοιχων με εκείνα του προσωπικού υπολογιστή (π.χ. αποστολή ηλεκτρονικής αλληλογραφίας, ηλεκτρονικός υπολογιστής, επεξεργασία κειμένου, λογιστικών φύλων, παιχνιδιών, αναπαραγωγή πολυμέσων, χρήση διαδικτύου) είναι ενσωματωμένο, αφού δεν ακολουθεί τον παραπάνω ορισμό;

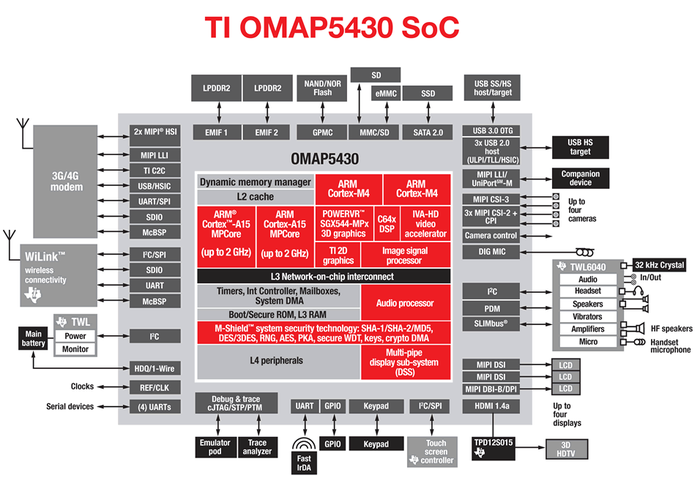

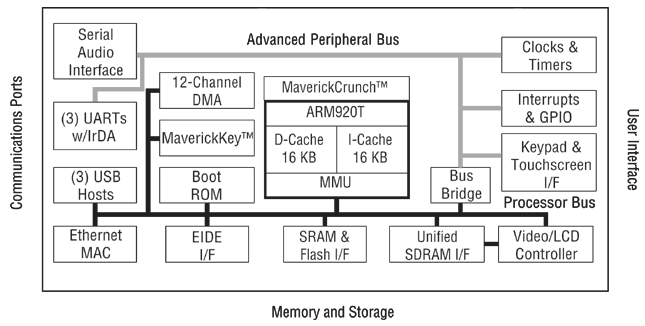

Ένας πιο αυστηρός ορισμός είναι ότι τα ενσωματωμένα συστήματα είναι εξειδικευμένα συστήματα υπολογιστών, τα οποία είναι αφοσιωμένα στην εκτέλεση μιας συγκεκριμένης λειτουργίας. Είναι συνδυασμός υλικού και λογισμικού μέρους. Μάλιστα, είναι κοινή πρακτική για τα ενσωματωμένα συστήματα η τοποθέτηση πάνω στην ίδια επιφάνεια πυριτίου επεξεργαστικών πυρήνων, μνημών, περιφερειακών, διασυνδέσεων εισόδου/εξόδου και μερικές φορές αναλογικών/ψηφιακών κυκλωμάτων, καταλήγοντας σε ολόκληρα συστήματα πάνω στο ίδιο υλικό πυριτίου (System-on-Chip, SOC). Συνήθως, τα ενσωματωμένα συστήματα είναι τμήμα ενός μεγαλύτερου συστήματος ή προϊόντος.

Πάντως, υπάρχουν μερικά σαφή χαρακτηριστικά σχετικά με τα ενσωματωμένα συστήματα. Έτσι, τα ενσωματωμένα συστήματα έχουν μια συγκεκριμένη λειτουργία. Ένα ενσωματωμένο σύστημα σχεδιάζεται για μια μόνο λειτουργία και την εκτελεί αδιαλείπτως. Γι αυτό και μερικές φορές ονομάζεται και ‘αποκλειστικό’ σύστημα. Ένα ενσωματωμένο σύστημα δεν μπορεί να χρησιμοποιηθεί για λειτουργίες διαφορετικές από αυτές που έχει σχεδιαστεί να επιτελέσει. Για παράδειγμα, δε θα μπορούσαμε να χρησιμοποιήσουμε τον ενσωματωμένο επεξεργαστή ενός έξυπνου πλυντηρίου, για να αναπαράγουμε πολυμέσα. Επίσης, τα ενσωματωμένα συστήματα έχουν αυξημένους περιορισμούς. Αν και κάθε υπολογιστικό σύστημα έχει περιορισμούς στο σχεδιασμό, τα ενσωματωμένα συστήματα πρέπει να έχουν όσο το δυνατόν μικρότερο κόστος σχεδιασμού (αφού κατασκευάζονται σε μεγάλες ποσότητες και πρέπει να είναι φθηνά, ώστε να τα προτιμήσουν οι καταναλωτές), να έχουν υψηλές επιδόσεις (ώστε να ανταποκρίνονται αμέσως στις εντολές του χρήστη και να παρουσιάζουν μεγάλη διαδραστικότητα με αυτόν), να έχουν μικρό μέγεθος (αφού συχνά βρίσκονται σε φορητές συσκευές), να έχουν μικρή κατανάλωση ενέργειας (αφού από τη μια πρέπει να λειτουργούν συνέχεια και από την άλλη να μην απαιτείται κάποια μέθοδος ψύξης), και να έχουν μεγάλη αξιοπιστία (δηλαδή να έχουν απρόσκοπτη λειτουργία). Ακόμη, θα μπορούσαμε να πούμε ότι τα ενσωματωμένα συστήματα βασίζονται σε ένα πλήθος επεξεργαστών (από διάφορες εταιρείες) και αρχιτεκτονικών. Έτσι, ενώ ένας προσωπικός υπολογιστής συνήθως αποτελείται από επεξεργαστές της εταιρείας AMD, ή της INTEL, τα ενσωματωμένα συστήματα συναντώνται με ένα πλήθος επεξεργαστών. Ένα ακόμη χαρακτηριστικό των ενσωματωμένων συστημάτων είναι το λειτουργικό που έχουν, που σχεδόν πάντα είναι ένα λειτουργικό πραγματικού χρόνου (Real Time Operating System - RTOS). Σε αντίθεση με τα κλασσικά λειτουργικά συστήματα (π.χ. Windows, Linux, FreeBSD) που συναντώνται σε προσωπικούς υπολογιστές, τα λειτουργικά των ενσωματωμένων συστημάτων λαμβάνουν πάντα σοβαρά υπόψη τις προτεραιότητες των εφαρμογών, και δίνουν όλη την επεξεργαστική ισχύ τους σε εφαρμογές με υψηλή προτεραιότητα. Ο σχεδιαστής είναι υπεύθυνος για να δώσει (ή να αφαιρέσει) προτεραιότητες στις εφαρμογές του συστήματος. Αν το κάνει σωστά, τότε τα λειτουργικά συστήματα των ενσωματωμένων αποδεικνύονται πολύ πιο σταθερά και αξιόπιστα, σε σύγκριση με τα λειτουργικά των προσωπικών υπολογιστών. Μια άλλη διαφοροποίηση είναι ότι το λειτουργικό σύστημα των ενσωματωμένων συστημάτων έχει πολύ μικρό μέγεθος (μερικά KB) και για αυτό τον λόγο δεν είναι και φιλικό προς τον χρήστη (user friendly) ή τον προγραμματιστή. Τέλος, το λειτουργικό σύστημα και οι εφαρμογές των ενσωματωμένων συστημάτων βρίσκονται τοποθετημένα σε μνήμη ROM, που ονομάζεται και μνήμη εντολών. Αντιθέτως, το λειτουργικό σύστημα ενός προσωπικού υπολογιστή, ή ενός διακομιστή, βρίσκεται σε κάποια αποθηκευτική μονάδα δίσκου (λόγω του υπερβολικά μεγάλου μεγέθους που έχει) και είναι πολύ εύκολο να τροποποιηθεί. Για να αλλάξει το λογισμικό του ενσωματωμένου, πρέπει να αντικατασταθεί η μνήμη ROM με μια άλλη που έχει το καινούργιο πρόγραμμα, μια διαδικασία που απαιτεί εξειδικευμένο προσωπικό. Ασφαλώς, τα τελευταία χρόνια φαίνεται πως τροποποιείται το τοπίο ως προς τη μνήμη, και έτσι πολλά ΕΣ έχουν αντί για μνήμη ROM μνήμη FLASH ή EEPROM, η οποία επιτρέπει την εύκολη αναβάθμιση του συστήματος σε περίπτωση ανάγκης.

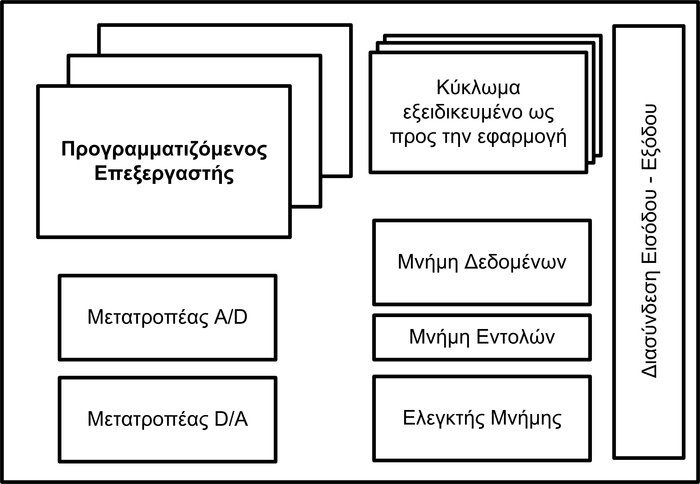

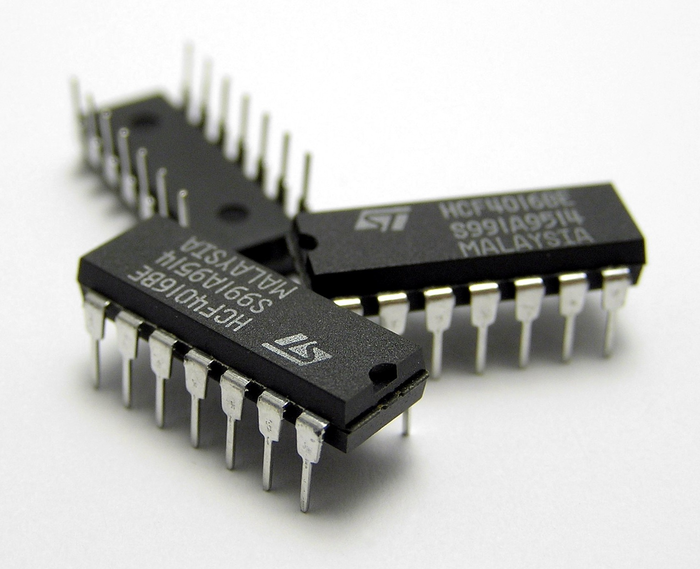

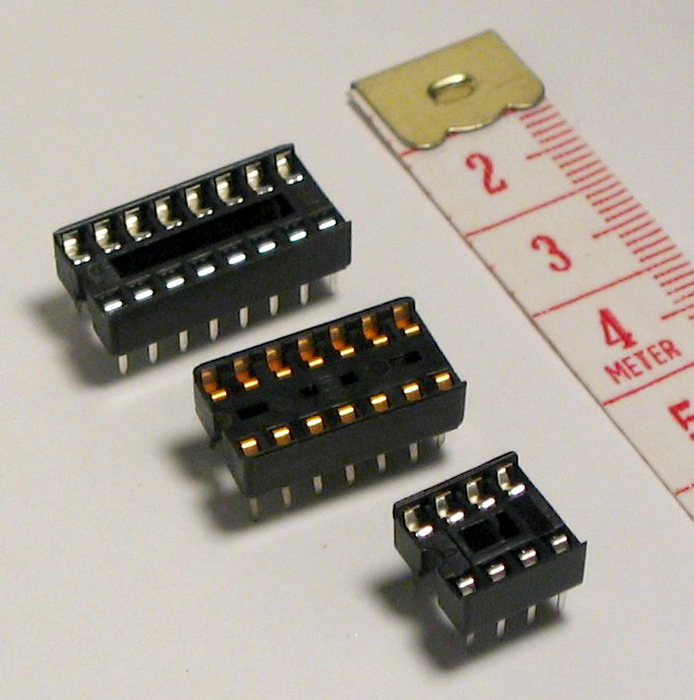

1.10: Ένα τυπικό ενσωματωμένο σύστημα αποτελείται από διακριτά δομοστοιχεία.

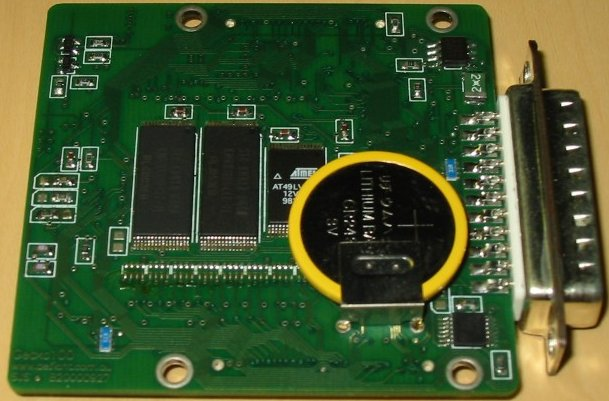

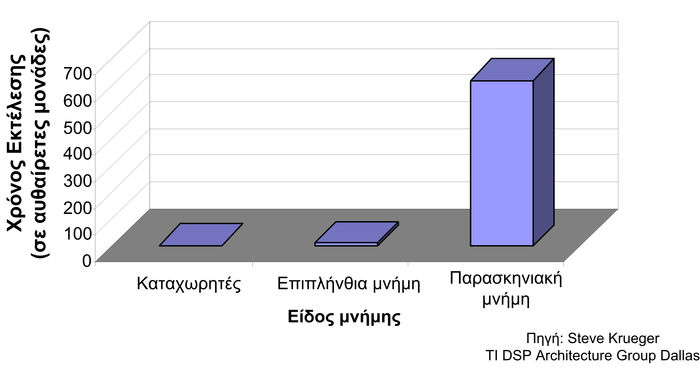

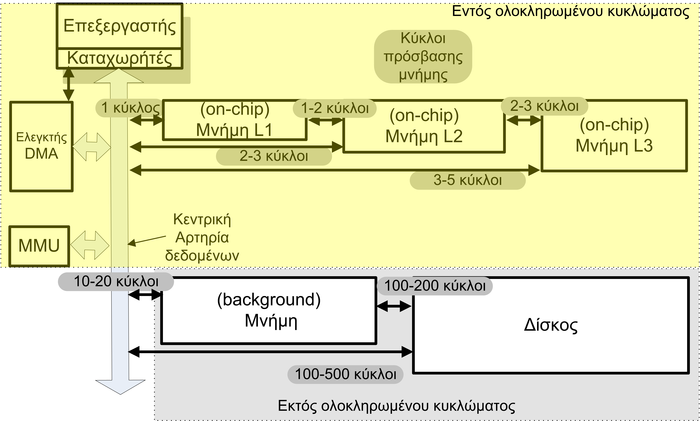

Ένα ενσωματωμένο σύστημα αποτελείται συχνά από πολλά τμήματα. Το σχήμα 1.10 παρουσιάζει τα δομοστοιχεία, που μαζί συνθέτουν ένα τυπικό ενσωματωμένο σύστημα. Συνήθως, ένα ενσωματωμένο σύστημα αποτελείται από έναν ή περισσότερους επεξεργαστές, από τους μετατροπείς αναλογικού σήματος σε ψηφιακό (A/D converter), από μετατροπείς ψηφιακού σήματος σε αναλογικό (D/A converter), από τη μνήμη εντολών που έχει το λογισμικό του συστήματος, τη μνήμη δεδομένων όπου αποθηκεύονται ή διαβάζονται δεδομένα, από κυκλώματα εξειδικευμένα ως προς την εφαρμογή που εκτελείται, από τον ελεγκτή της μνήμης δεδομένων και, τέλος, τη διασύνδεση εισόδου-εξόδου. Η μνήμη εντολών του επεξεργαστή βρίσκεται εκτός ολοκληρωμένου κυκλώματος, επειδή μπορεί να χρειαστεί να γίνει κάποια μικρή τροποποίηση της λειτουργίας του. Επίσης, η μνήμη δεδομένων αποτελείται συνήθως από μνήμη πάνω στο ολοκληρωμένο κύκλωμα και από κάποια παρασκηνιακή μνήμη.

Τα πιο σημαντικά δομοστοιχεία που έχει ένα ενσωματωμένο σύστημα είναι ο μικροεπεξεργαστής και η μνήμη. Η σημαντικότητά τους οφείλεται στο γεγονός ότι ο σχεδιασμός και η χρήση αυτών, επηρεάζουν σημαντικά την επίδοση και την κατανάλωση ενέργειας του συστήματος.

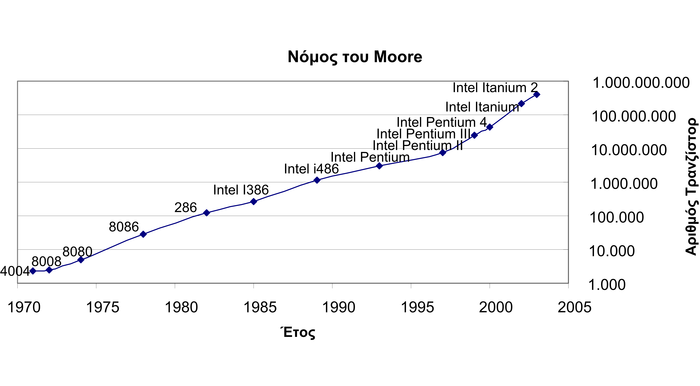

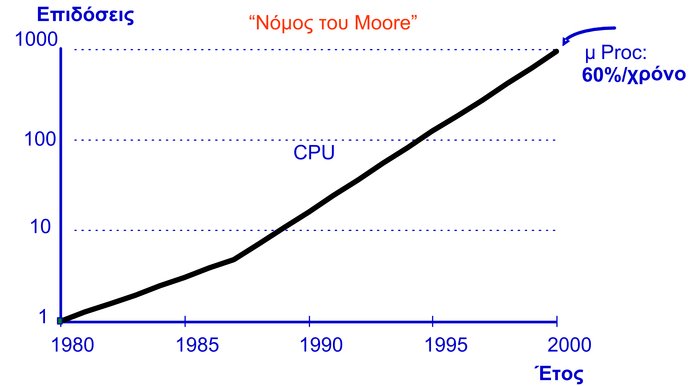

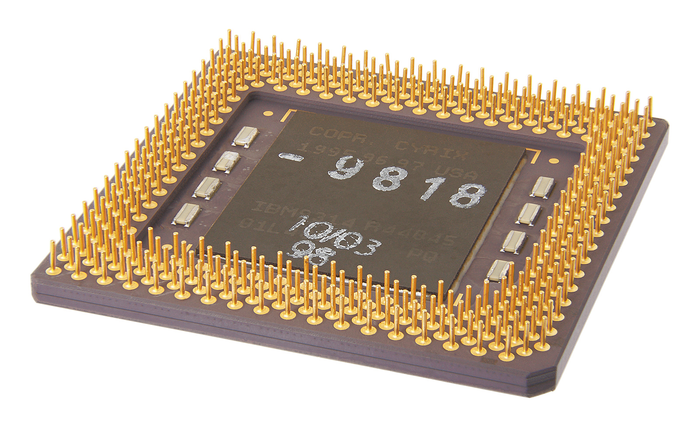

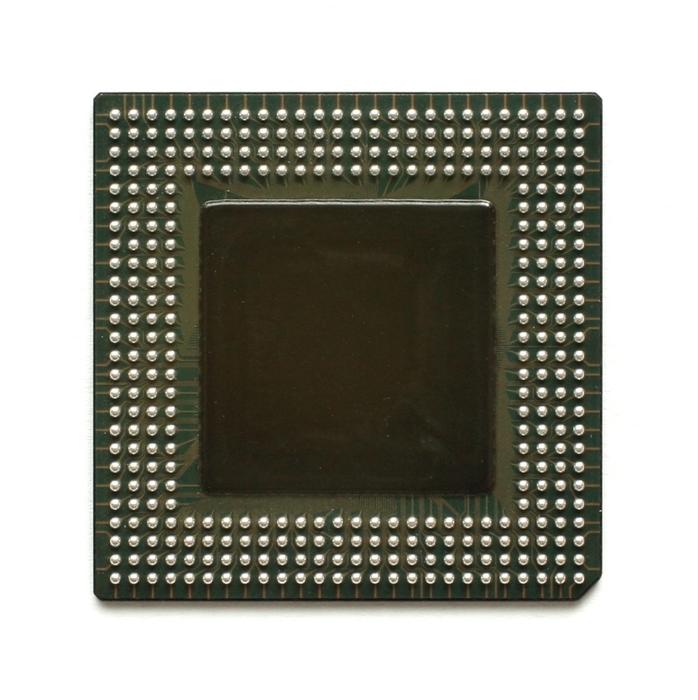

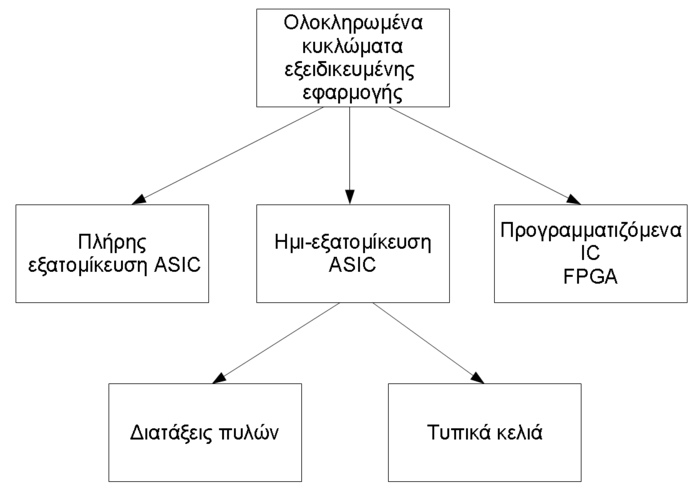

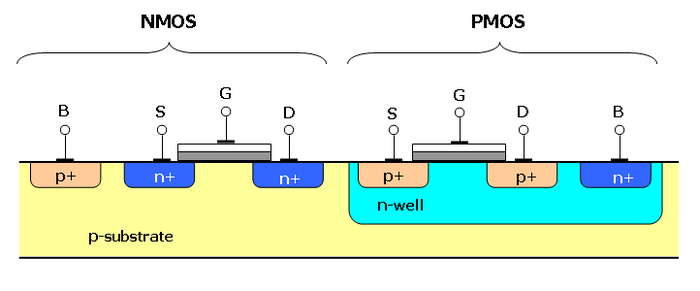

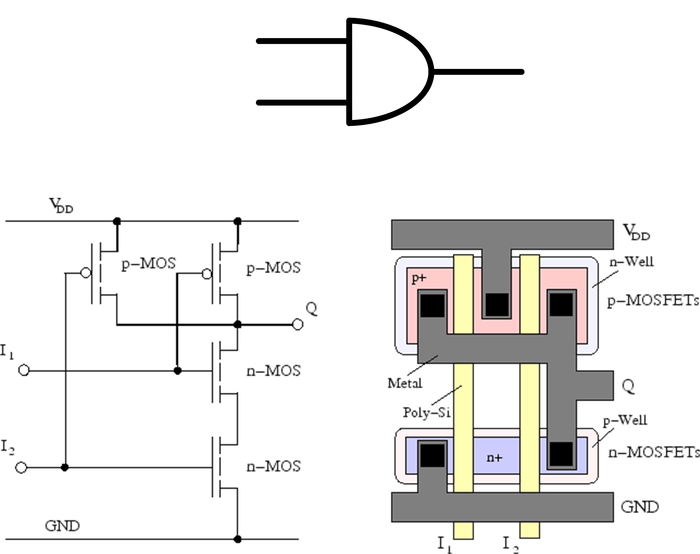

Ο μικροεπεξεργαστής έχει εξελιχθεί σημαντικά, και ενώ αρχικά αποτελούνταν από μερικές χιλιάδες τρανζίστορ, τώρα έχει κοντά στα 100-400 εκατομμύρια τρανζίστορ πάνω στο ίδιο ολοκληρωμένο κύκλωμα (για παράδειγμα Alpha 21364 [3], Pentium 4 [4], Athlon XP [5] και άλλοι). Η σημαντική πρόοδος που επιτελέστηκε στους επεξεργαστές, έκανε προσιτά στο καταναλωτικό κοινό (και με χαμηλό κόστος) τα ενσωματωμένα συστήματα. Η πολυπλοκότητα των παραπάνω επεξεργαστών, σε συνδυασμό με μονάδες μνήμης που περιέχουν πάνω από 256 εκατομμύρια στοιχεία στο ίδιο ολοκληρωμένο κύκλωμα, έχουν κάνει δυνατό το σχεδιασμό ολόκληρων συστημάτων ως ένα ολοκληρωμένο κύκλωμα (System On Chip, SOC). Αυτό ξεφεύγει από τον κλασσικό σχεδιασμό ASIC (Application-Specific Integrated Circuit), αφού για παράδειγμα είμαστε σε θέση να υλοποιήσουμε όλες τις λειτουργίες βασικής ζώνης ενός κινητού τηλεφώνου σε ένα μόνο ολοκληρωμένο κύκλωμα.

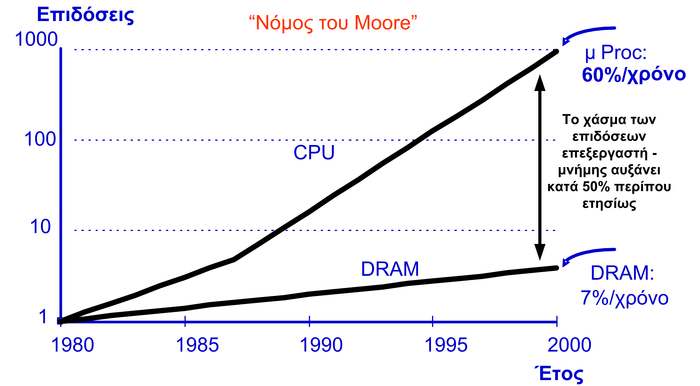

Σε αντίθεση με τον επεξεργαστή, το άλλο σημαντικό δομοστοιχείο ενός ενσωματωμένου συστήματος, δηλαδή η μνήμη εντός και εκτός ολοκληρωμένου κυκλώματος, δεν έχει ακολουθήσει τους ίδιους ρυθμούς ανάπτυξης. Αυτά τα δύο γεγονότα, έχουν δημιουργήσει ένα ολοένα αυξανόμενο χάσμα ανάμεσα στις συχνότητες λειτουργίας του επεξεργαστή και της μνήμης, το οποίο δημιουργεί αρκετά προβλήματα, ειδικά σε εφαρμογές που έχουν αυξημένες απαιτήσεις πρόσβασης στη μνήμη.

Όμως, μαζί με την ανάπτυξη των ενσωματωμένων συστημάτων υπήρξε και μια ανάπτυξη στην πολυπλοκότητα των εφαρμογών που εκτελούνται από αυτά. Αν και δεν είναι σαφές αν η τεχνολογία είναι αυτή που προώθησε την ανάπτυξη τόσο πολύπλοκων εφαρμογών, ή οι επεξεργαστικές απαιτήσεις των εφαρμογών πίεσαν τους μηχανικούς να σχεδιάσουν καλύτερα συστήματα· εντούτοις, έχουμε φτάσει σε μια εποχή που η επεξεργαστική πολυπλοκότητα των εφαρμογών είναι αρκετά μεγάλη. Μερικές φορές είναι αδύνατον κάποιες εφαρμογές να εκτελεστούν σε πραγματικό χρόνο με τη χρήση των σημερινών ενσωματωμένων συστημάτων.

Σε αυτή την ενότητα θα παρουσιάσουμε 3 σχεδιαστικά παραδείγματα για να γίνουν κατανοητές οι ανάγκες ελέγχου και υπολογισμών που διέπουν τα ενσωματωμένα συστήματα, με διάφορους βαθμούς πολυπλοκότητας. Ένα απλό ΕΣ που βρίσκεται σε μια επαγωγική κουζίνα, ένα μεσαίας πολυπλοκότητας ΕΣ που βρίσκεται μέσα σε ένα ψηφιακό καταγραφέα αυτοκινήτου (CAR DVR) και ένα υψηλής πολυπλοκότητας ΕΣ που βρίσκεται μέσα σε ένα αυτοκίνητο.

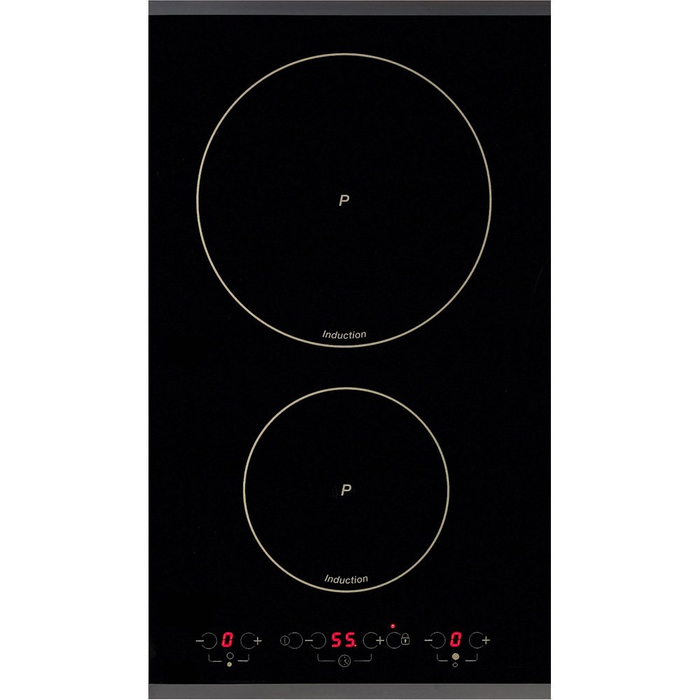

Σε μια σύγχρονη οικία, κάποιος μπορεί να διακρίνει ενσωματωμένα συστήματα σε πλήθος συσκευών. Μια από αυτές τις συσκευές είναι η επαγωγική εστία (Εικόνα 1.11). Στο παρελθόν χρησιμοποιούνταν κεραμικές κουζίνες με περιστροφικούς διακόπτες, οι οποίες ασφαλώς δεν ήταν ενσωματωμένα συστήματα. Η ρύθμιση της θερμοκρασίας γίνονταν με κάποιο διμεταλλικό έλασμα που μόλις ζεσταίνονταν σε κάποια θερμοκρασία, έκοβε το ρεύμα που διέρρεε από την αντίσταση. Ο περιστροφικός διακόπτης ρύθμιζε την απόσταση από το διμεταλλικό έλασμα και την επαφή στην αντίσταση. Δεν υπήρχε κάποιο πρόγραμμά ή κάποια παραπάνω ανάγκη. Προκειμένου οι κατασκευαστές να βελτιώσουν το σχεδιασμό της κουζίνας και να προσθέσουν στυλ, αλλά ταυτόγχρονα να δώσουν και παραπάνω δυνατότητες ξανασχεδίασαν το σύστημα με τη χρήση ενός ΕΣ.

Οι δυνατότητες που παρέχει το νέο ΕΣ είναι οι εξής:

Τα κουμπιά δεν είναι περιστροφικά, αλλά αισθητήρια απόστασης τα οποία κρύβονται κάτω από το γυαλί της εστίας και εκπέμπουν μια υπεριώδη ακτινοβολία, όπου ανιχνεύουν την αντανάκλαση. Ο χρήστης αρκεί να τοποθετήσει το δάκτυλο πάνω από το αισθητήριο και μέσω της αντανάκλασης στο δάχτυλο του θα ανιχνευθεί η επιλογή. Αντικαταστάθηκαν λοιπόν, οι περιστροφικοί διακόπτες με αυτούς τους οπτικούς αισθητήρες ανάκλασης (reflective optical sensors), εμείς θα τους καλούμε διακόπτες ανάκλασης ή απλώς διακόπτες.

Επιλογή του ‘ματιού’ της κουζίνας που θα θερμανθεί.

Επιλογή θερμοκρασίας μέσω κουμπιών αύξησης ή μείωσης (από 0, που είναι σβηστό, έως 9 που είναι το μέγιστο), για το συγκεκριμένο μάτι.

Ηχητική ένδειξη για κάθε επιλογή με beeper (κάθε φορά που ο χρήστης επιλέγει κάτι).

Φωτεινή ένδειξη με οθόνες 7 στοιχείων (7 segments display) για κάθε μάτι που δείχνει τον αριθμό που έχει επιλεγεί, ενώ επίσης χρησιμοποιείται η τελεία για να σηματοδοτεί το μάτι που έχει επιλεχθεί.

Ρύθμιση της θερμοκρασίας μέσω PWM (pulse width modulation, διαμόρφωση πλάτους παλμού), όπου αναλόγως της επιλογής της θερμοκρασίας, διαμορφώνεται κατάλληλα ο κύκλος ενεργοποίησης και απενεργοποίησης. Π.χ. για θερμοκρασία στο επίπεδο 1, σημαίνει ότι η αντίσταση στο μάτι θα είναι 10% ενεργοποιημένη και 90% απενεργοποιημένη, ενώ στη μέγιστη βαθμίδα 9, θα είναι 100% ενεργοποιημένη.

Κλείδωμα των επιλογών μέσω ειδικού διακόπτη, όπου απαιτείται παρατεταμένη επιλογή του κατάλληλου διακόπτη για να αρθεί το κλείδωμα. Το κλείδωμα χρησιμοποιείται για να ακυρώνει τις λειτουργίες των άλλων διακοπτών, ώστε να μη πατηθούν κατά λάθος (π.χ. αν αφήσει κάποιος κάτι στην κουζίνα).

Οι απαιτήσεις του προγράμματος δε συνοδεύονται από αυστηρούς χρονικούς περιορισμούς (δεν απαιτείται να ενεργοποιηθεί η αντίσταση μέσα σε XX ns, αν ενεργοποιηθεί λίγο αργότερα δεν υπάρχει πρόβλημα), ούτε από ενεργειακούς περιορισμούς (η εστία τροφοδοτείται από εναλλασσόμενο ρεύμα 230V, και το 99% καταναλώνεται στις αντιστάσεις των ματιών), ούτε από θέμα κόστους (το κόστος των ηλεκτρονικών στοιχείων είναι αμελητέο ως προς την υπόλοιπη κατασκευή). Γενικά, ο σχεδιασμός ενός ΕΣ για αυτό το σύστημα είναι αρκετά απλός και εύκολος. Η μόνη απαίτηση είναι ο μικροεπεξεργαστής να έχει αρκετές εισόδους/εξόδους για να καλύψει τις ανάγκες.

1.11: Μια σύγχρονη επαγωγική εστία φέρει ένα ενσωματωμένο σύστημα.

Επειδή οι ανάγκες είναι αρκετά απλές, συνήθως οι κατασκευαστές επιλέγουν τον πιο απλό επεξεργαστή, έναν 8bit στα 16Mhz (συγκρίνετε τους επεξεργαστές στους επιτραπέζιους ή φορητούς υπολογιστές που διαχειρίζονται 64bit στα 1.5 με 2 Ghz). Ο επεξεργαστής θα πρέπει να έχει εσωτερική μνήμη FLASH για να μπορεί να διατηρεί το πρόγραμμα (32ΚΒ μνήμη FLASH είναι υπεραρκετά). Η μνήμη θα μπορούσε να είναι και εξωτερική, αλλά δεν υπάρχει διαφορά στο κόστος και προτιμάται ο επεξεργαστής να έχει εσωτερική μνήμη. Η μνήμη RAM του μικροεπεξεργαστή αρκεί να είναι κάποια Byte (π.χ. 1 ή 2 KB είναι αρκετά). Ως προς τους ακροδέκτες του μικροεπεξεργαστή, κάθε οθόνη 7 στοιχείων μαζί με την τελεία, απαιτεί 8 εξόδους, το beeper απαιτεί 1 έξοδο, κάθε διακόπτης απαιτεί 1 είσοδο, και κάθε αντίσταση έχει ένα ρελέ που ελέγχει τη ροή του ρεύματος, οπότε συνολικά ο μικροεπεξεργαστής για 2 μάτια πρέπει να υποστηρίζει 2*8 + 1 +2 εξόδους και 6 εισόδους, συνολικά 23. Μάλιστα, για να μειωθούν οι απαιτήσεις σε ακροδέκτες, μπορούν να χρησιμοποιηθούν 2 των 8bit εξωτερικοί σειριακοί καταχωρητές παράλληλης εξόδου συνδεδεμένοι σε σειρά, που χρησιμοποιούν 3 ακροδέκτες από τον μικροεπεξεργαστή (και όχι 2*8), οπότε οι συνολικές ανάγκες του συστήματος είναι 3 + 1 + 2+ 6 = 12 ακροδέκτες. Εκτός από τις παραπάνω συνδέσεις, θα απαιτηθούν και οι κατάλληλες αντιστάσεις pull-up ή pull-down, o σχεδιασμός του PCB (printed circuit board, τυπωμένη πλακέτα κυκλώματος), η δρομολόγηση των ασθενών και ισχυρών ρευμάτων και η κατάλληλη θωράκιση από παρεμβολές για να είναι σύμφωνη με το πρότυπο της ηλεκτρομαγνητικής θωράκισης. Ασφαλώς δε χρειάζεται λειτουργικό σύστημα το ΕΣ, και αρκεί να γραφεί ένα πρόγραμμα είτε σε γλώσσα μηχανής, είτε στην πιο φιλική C, όπως συνηθίζεται Το πρόγραμμα θα αποτελείται από έναν αέναο βρόχο που θα κάνει διαδοχική σταθμοσκόπηση των επιλογών των διακοπτών, θα ενημερώνει κατάλληλα τις οθόνες 7 στοιχείων, θα ενεργοποιεί το beeper, και θα διαμορφώνει μέσω PWM τη θερμοκρασία.

Ο κατασκευαστής της κουζίνας μπορεί να παρέχει για την ίδια κουζίνα πολλαπλές δυνατότητες. Εκτός από το παραπάνω που είναι το βασικό μοντέλο, θα μπορούσε να προσθέσει ένα δομοστοιχείο bluetooth (που απαιτεί 2 ακροδέκτες RX/TX, για σειριακή επικοινωνία με τον μικροεπεξεργαστή), και να δίνει μια εφαρμογή για έξυπνα κινητά, ώστε η ρύθμιση της θερμοκρασίας να γίνεται με ακόμη πιο φιλικό τρόπο ή θα μπορούσε να τοποθετήσει ένα δομοστοιχείο επικοινωνίας wifi 802.11 για σύνδεση στο διαδίκτυο, ώστε να στέλνει ενημερώσεις με email ή να υπάρχει έλεγχος από κεντρικό website. Ασφαλώς, το κάθε μοντέλο επαγωγικής κουζίνας θα έχει και την ανάλογη τιμή, που συνήθως είναι πολλαπλάσια από το κόστος του υλικού (π.χ. ένα δομοστοιχείο bluetooth κοστίζει 5 ευρώ, ενώ ο κατασκευαστής της κουζίνας μπορεί να χρεώνει αυτό το μοντέλο 150 ευρώ παραπάνω από το βασικό). Βέβαια το πως διαμορφώνεται το κόστος αποτελεί μελέτη της επόμενης ενότητας.

Ένα αρκετά δημοφιλές ΕΣ είναι ο ψηφιακός καταγραφέας υψηλής ανάλυσης (High Definition DVR), ο οποίος τοποθετείται με μια βεντούζα στο παρμπρίζ του αυτοκινήτου και καταγράφει τη διαδρομή. Αυτή η καταγραφή μπορεί να χρησιμοποιηθεί ως αποδεικτικό στοιχείο σε περίπτωση τρακαρίσματος, για να καθοριστεί ο υπαίτιος. Σε σύγκριση με το προηγούμενο ΕΣ, αυτό έχει υψηλότερες απαιτήσεις, όπως φαίνονται από τη λίστα που ακολουθεί:

Αποθήκευση VIDEO σε υψηλή ανάλυση σε κάρτα Micro SD.

Συμπίεση VIDEO κατά H.234 σε πραγματικό χρόνο για μείωση των απαιτήσεων χώρου.

Χαμηλή κατανάλωση ενέργειας (έως 1 A στα 12V, όσο παρέχει η σύνδεση του εσωτερικού αναπτήρα αυτοκινήτου).

Πλήθος κουμπιών ελέγχου.

Ρολόι πραγματικού χρόνου με διατήρηση της ημερομηνίας.

Εσωτερική μπαταρία LiPO με κύκλωμα φόρτισης μέσω mini USB.

Μενού με ποικίλες ρυθμίσεις ποιότητας και διαχείρισης της κάρτας SD.

Μετατροπέας Αναλογικού σε Ψηφιακό, για την διασύνδεση με τον οπτικό αισθητήρα CMOS ή CCD.

Υποστήριξη LCD (liquid crystal display) για την εμφάνιση του video και των ρυθμίσεων.

Δημιουργία συμβατού συστήματος αρχείου FAT στην κάρτα SD, ώστε να μπορεί να διαβαστεί από ένα PC

Υποστήριξη για USB Mass Storage Device όταν συνδέεται σε ένα PC

Πολύ μικρό μέγεθος, ώστε να μην επηρεάζει το οπτικό πεδίο του χρήστη (αφού τοποθετείται στο μπροστινό παρμπρίζ).

1.12: Ένας ψηφιακός καταγραφέας αυτοκινήτου υψηλής ανάλυσης αποτελεί ένα μεσαίας πολυπλοκότητας ΕΣ.

Όπως φαίνεται από τις απαιτήσεις, το σύστημα αυτό είναι πιο πολύπλοκο από το απλό ΕΣ που χρησιμοποιείται σε μια επαγωγική κουζίνα. Η πιο σημαντική απαίτηση είναι η ύπαρξη αυστηρών περιορισμών χρόνου και συγκεκριμένα η ανάγνωση μιας εικόνας υψηλής ανάλυσης (1080p, δηλαδή 1920x1080 στα 3x8=24 bit), σε ρυθμό 25 FPS (frames per second, εικονοστοιχεία το δευτερόλεπτο), συμπίεση και αποθήκευση σε ένα μέσο αποθήκευσης. O επεξεργαστής θα πρέπει να είναι 32bit (διαφορετικά με 8bit θα υπήρχε μεγάλη καθυστέρηση) και για να επιτευχθεί η χαμηλή κατανάλωση και ο μικρός όγκος, θα πρέπει να ενσωματώνει τις περισσότερες λειτουργίες πάνω στο ίδιο ολοκληρωμένο κύκλωμα (SoC, System On Chip - σύστημα πάνω στο ίδιο chip). Θα πρέπει να χρησιμοποιηθεί είτε ένας δυνατός 32bit επεξεργαστής, συνήθως της εταιρίας ARM, ή ένας άλλος 32bit επεξεργαστής, με έναν επιταχυντή υλικού για τη λειτουργία της συμπίεσης Η.234 σε πραγματικό χρόνο. Θα πρέπει το ίδιο SoC να υποστηρίζει USB για mass storage device (υποστήριξη σύνδεσης σε υπολογιστή ως δίσκο), και να έχει έναν ελεγκτή για μνήμες SD. Για να διατηρείται η ώρα, θα πρέπει να υπάρχει ένα κύκλωμα RTC (real time clock, ρολόι πραγματικού χρόνου) στο ίδιο το SoC (ή εκτός), το οποίο θα τροφοδοτείται από συγκεκριμένο ακροδέκτη του επεξεργαστή από τη μπαταρία της συσκευής και θα συνδέεται μέσω ενός διαύλου με τον επεξεργαστή. Κάθε φορά που ο επεξεργαστής ζητάει να ενημερωθεί για την τρέχουσα ώρα (π.χ. κατά την ενεργοποίηση του συστήματος), θα δίνεται αυτή η ενημέρωση, όπως επίσης θα υπάρχει δυνατότητα της ρύθμισης του RTC σε μια συγκεκριμένη ώρα. Το SoC θα πρέπει να έχει και τον ελεγκτή για το LCD, ενώ τα κουμπιά θα πρέπει να συνδεθούν είτε κατευθείαν σε ακροδέκτες του SoC, είτε σε ένα ξεχωριστό περιφερειακό Ι/Ο, που συνδέεται με τον επεξεργαστή. Επίσης, απαιτούνται πυκνωτές και αντιστάσεις για το κύκλωμα φόρτισης και προστασίας της μπαταρίας, όπως και για τη διασύνδεση των περιφερειακών. Αυτό το ΕΣ μπορεί να υλοποιηθεί είτε αποκλειστικά σε C χωρίς λειτουργικό σύστημα, το οποίο είναι αρκετά πολύπλοκο αλλά όχι αδύνατο, αφού θα πρέπει να υλοποιήσει ο σχεδιαστής το λογισμικό οδήγησης για κάθε ελεγκτή (LCD, H.234, CCD/CMOS, κ.α.), να σχεδιάσει τη γραφική διεπαφή χρήστη και να υλοποιήσει το λογισμικό τμήμα του USB, για τη διασύνδεση με τον υπολογιστή, ώστε να φαίνεται ως μια συσκευή USB Mass Storage Device. Αυτή η σχεδίαση που ονομάζεται ‘bare metal programming’, είναι η πιο δύσκολη, αλλά έχει ως αποτέλεσμα την καλύτερη εκμετάλλευση των πόρων. Μια εναλλακτική σχεδίαση αποτελεί η χρήση ενός λειτουργικού συστήματος, π.χ. Linux, που έχει έτοιμες βιβλιοθήκες για πολλές λειτουργίες. Το μειονέκτημα με το λειτουργικό σύστημα είναι ότι ίσως απαιτηθεί πιο γρήγορος επεξεργαστής και περισσότερη μνήμη, αφού το ΛΣ θα χρησιμοποιεί κάποιους από τους πόρους του συστήματος. Η ανάπτυξη του λογισμικού όταν υπάρχει ένα ΛΣ γίνεται πολύ πιο εύκολη, αφού το ΛΣ παρέχει στον προγραμματιστή μια αφαιρετική εικόνα για το hardware, και έτσι δε χρειάζεται να γνωρίζει λεπτομέρειες σχετικά με το υλικό, αρκεί να χρησιμοποιεί τις τυπικές διεπαφές του ΛΣ.

Ένα από τα πιο σύνθετα ΕΣ βρίσκεται σε ένα σύγχρονο αυτοκίνητο. Θα πρέπει να σημειωθεί ότι σε αυτή την περίπτωση δεν υπάρχει μόνο ένα ΕΣ, αλλά πλήθος ΕΣ, που συνεργάζονται μεταξύ τους για την επίτευξη του επιθυμητού αποτελέσματος, το οποίο είναι η επίτευξη υψηλής ασφάλειας και άνεσης για τους επιβάτες. Επειδή όλα αυτά τα συστήματα συνεργάζονται μεταξύ τους, εμείς θα τα θεωρήσουμε ως ένα μεγάλο ΕΣ. Επιπρόσθετα, τα ΕΣ γνώρισαν μεγάλη ανάπτυξη κατά τη δεκαετία του 1970, όταν προέκυψε η πετρελαϊκή κρίση και έτσι οι κατασκευαστές αυτοκινήτων ερεύνησαν πως θα μπορούσαν να μειώσουν την κατανάλωση καυσίμου, και που το πέτυχαν με την τοποθέτηση ψηφιακών συστημάτων μέσα στο αυτοκίνητο που ρύθμιζε κάθε στάδιο λειτουργίας του κινητήρα και βελτιστοποιούσε την καύση.

Οι λειτουργίες του ΕΣ σε ένα σύγχρονο αυτοκίνητο είναι:

Βελτιστοποίηση της καύσης καυσίμου.

Έλεγχος οδήγησης cruise (adaptive cruise control, ACC).

Προειδοποίηση σύγκρουσης (forward collision warning, FCW).

Προειδοποίηση αποχώρησης λωρίδας (Lane Departure Warning, LDW).

Σύστημα βοήθειας στο παρκάρισμα (Park Assist System, PAM).

Σύστημα παρακολούθησης πίεσης ελαστικών (Time Pressure Monitoring System, TPMS).

Ξεκλείδωμα χωρίς κλειδί (Remote Keyless Entry).

Διασύνδεση με bluetooth, wifi, GSM.

Πλοήγηση με GPS.

Έλεγχος ραδιόφωνου (π.χ. όταν λαμβάνει μια κλήση μέσω bluetooth να μειώνεται η ένταση).

Σύστημα αντιμπλοκαρίσματος τροχών (Antilock braking system, ABS).

Έλεγχος ταχύτητας (Wheel Speed Sensor).

Κάμερα οπισθοπορείας (rear view camera).

Ηλεκτρικό Τιμόνι (electric power steering) για τη βοήθεια στο παρκάρισμα.

Έλεγχος αερόσακων (airbags).

Έλεγχος ζώνης (seatblet pretensionner).

Μπροστινό Radar για άμεση ενεργοποίηση φρένων.

Διαγνωστικά αισθητηρίων (sensor diagnostics).

Multimedia System

.....(και πολλά άλλα)

Είναι εμφανές ότι ένα τέτοιο σύστημα έχει πολλές και πολύπλοκες απαιτήσεις, άλλες που απαιτούν απόκριση σε πραγματικό χρόνο (π.χ. τo ABS), και άλλες που είναι πιο ανεκτικές ως προς τις αποκρίσεις (π.χ. GPS). Επίσης, είναι εμφανές ότι ένα τέτοιο σύστημα δε μπορεί να υποστηριχθεί από ένα μόνο επεξεργαστή, αλλά απαιτούνται πολλαπλοί επεξεργαστές, διάσπαρτοι σε διάφορα σημεία του οχήματος, οι οποίοι επικοινωνούν με ένα ή περισσότερα δίκτυα διασύνδεσης (θα αναλύσουμε τα δίκτυα διασύνδεσης σε άλλο κεφάλαιο). Το πιο δημοφιλές δίκτυο διασύνδεσης για τα οχήματα, είναι το CAN (controller area network, δίκτυο περιοχής ελεγκτών). Συνήθως, τα αυτοκίνητα έχουν ένα ή δυο δίκτυα CAN. Σε περίπτωση που έχουν δυο δίκτυα CAN, αυτά χρησιμοποιούνται ως εξής: Στο πρώτο δίκτυο CAN τοποθετούνται τα αισθητήρια και οι συσκευές δράσης που έχουν αυστηρούς περιορισμούς χρόνου (δηλαδή, από τη στιγμή που ανιχνευτεί μια δυσλειτουργία, θα πρέπει ο επεξεργαστής να τη χειριστεί άμεσα και να δώσει την κατάλληλη εντολή), όπως ABS, έλεγχος πέδησης, έλεγχος τιμονιού, έλεγχος φώτων, έλεγχος κινητήρα κ.α. Στο δεύτερο δίκτυο CAN τοποθετούνται αισθητήρια και οι συσκευές δράσεις (κυρίως ενδεικτικές λυχνίες) που έχουν πιο χαλαρούς περιορισμούς. Για παράδειγμα, το αισθητήριο των θυρών (ανοιχτές/κλειστές), της πρόσδεσης της ζώνης, του air-condition και των αισθητηρίων θερμοκρασίας κ.ο.κ. Με την πάροδο του χρόνου οι κατασκευαστές τοποθετούν όλο και περισσότερα αισθητήρια πάνω στους διαύλους CAN προκειμένου να κάνουν όσο το δυνατόν πιο φιλικά στη χρήση και στην οδήγηση, και πιο ασφαλή αυτοκίνητα, εμπλουτίζοντας τα με νέες δυνατότητες. Έτσι, ενώ στο παρελθόν τα αισθητήρια συνδέονταν άμεσα με τις ενδεικτικές λυχνίες στο ταμπλό, τώρα ενημερώνουν τον αντίστοιχο επεξεργαστή (που στην αυτοκινητοβιομηχανία ονομάζεται ECU, engine control unit- μονάδα ελέγχου μηχανής), και αυτός αποφασίζει τι θα εκτελεστεί. Για ένα τέτοιο ΕΣ απαιτείται ένα λειτουργικό σύστημα που σέβεται τις αυστηρές προθεσμίες (μια τυπική επιλογή είναι το λειτουργικό σύστημα QNX Neutrino RTOS), επεξεργαστές 32bit με γρήγορη εξυπηρέτηση διακοπών (π.χ. ARM), με μονάδα διαχείρισης μνήμης (MMU) ή μονάδα προστασίας μνήμης (MPU), αφού θα υπάρχουν αρκετές διεργασίες και θα πρέπει να είναι απομονωμένες, ώστε η μια να μη ‘μολύνει’ το χώρο μνήμης της άλλης, αρκετά μέτρα καλώδια για τα αισθητήρια, ένα λειτουργικό σύστημα για το 2ο δίκτυο (π.χ. Linux), που θα σχεδιαστούν οι γραφικές διεπαφές, και ο έλεγχος της τηλεματικής (τηλεματική είναι η αποστολή μέσω ασύρματου δικτύου δεδομένων σε απομακρυσμένη τοποθεσία· στο όχημα μπορεί να χρησιμοποιηθεί π.χ. για την αυτόματη αποστολή της θέσης στις πρώτες βοήθειες σε περίπτωση σύγκρουσης). Επίσης, θα πρέπει κάθε ηλεκτρονικό στοιχείο και αισθητήριο να υποστηρίζει αυτο-διάγνωση και ενημέρωση λειτουργίας και σε περίπτωση προβλήματος να μπορεί να μεταβεί σε μια ασφαλή κατάσταση, ώστε να μην επηρεάζει το υπόλοιπο όχημα. Σύμφωνα με τη νομοθεσία αρκετών χωρών, είναι υποχρεωτικό να ενημερώνεται ο οδηγός μέσω κατάλληλης λυχνίας MIL (malfunction indicator lamp, λυχνία ένδειξης δυσλειτουργίας) για την ύπαρξη οποιουδήποτε προβλήματος. Συστήματα άκρως απαραίτητα για την ασφάλεια, θα πρέπει να έχουν πλεονάζουσες (redundancy) επικοινωνίες, ώστε αν παρουσιάσει πρόβλημα το ένα κανάλι επικοινωνίας, να μπορεί να χρησιμοποιηθεί μια εναλλακτική διαδρομή. Το ΕΣ θα πρέπει να έχει επίσης μνήμη FLASH ή EEPROM, για να αποθηκεύει σε μη πτητικό μέσο (δηλαδή, που δε χάνει τα δεδομένα αν διακοπεί το ρεύμα), εκτός από τις ρυθμίσεις του χρήστη και το αρχείο καταγραφής βλάβης (fault log file), ώστε ο μηχανικός να μπορεί με το κατάλληλο μηχάνημα να ενημερωθεί με λεπτομέρειες για το πότε και υπό ποιες συνθήκες παρουσιάστηκε το σφάλμα. Τα αισθητήρια για το σύστημα των αυστηρά χρονικών προδιαγραφών, θα πρέπει να συνδέονται σε ξεχωριστή γραμμή διακοπής (interrupt line), ώστε να εξυπηρετούνται άμεσα αν χρειαστεί, ενώ τα αισθητήρια στο 2ο δίκτυο θα μπορούσαν να επικοινωνούν με κάποια διεργασία τύπου δαίμονα (daemon) που εκτελείται στο λειτουργικό σύστημα. Ασφαλώς, θα πρέπει να εξεταστεί ο χρόνος χείριστης εξυπηρέτησης (worst case service time), και να ελαχιστοποιηθεί, ώστε να μη διακυβεύεται η ασφάλεια. Η ανάπτυξη του λογισμικού θα πρέπει να γίνει σε μια γλώσσα υψηλού επιπέδου, εκτός από τις λειτουργίες που απαιτούν ελάχιστο χρόνο εξυπηρέτησης και μπορούν να προγραμματιστούν στη γλώσσα μηχανής του συγκεκριμένου επεξεργαστή.

Ένα σημαντικό στοιχείο για το σχεδιασμό των ΕΣ, όπως και κάθε άλλου προϊόντος, είναι το κόστος. Το συνολικό κόστος είναι το άθροισμα δυο επιμέρους κοστών: το μη επαναλαμβανόμενο κόστος μηχανικής (non recurrent engineering cost, NRE) και το κόστος μονάδας (unit cost).

Το NRE κόστος

περιέχει το κόστος που έχει δαπανήσει η εταιρία για την ανάπτυξη του συγκεκριμένου προϊόντος σε πληρωμές προσωπικού, σε σεμινάρια μηχανικών, σε αγορά ποικιλίας υλικών και δημιουργίας πρωτοτύπων, σε δοκιμές ποιότητας ή ηλεκτρομαγνητικής συμβατότητας, σε έξοδα των γραφείων (φως, νερό, θέρμανση, αναλώσιμα), σε ειδικό εξοπλισμό που απαιτήθηκε για τη δημιουργία του προϊόντος (π.χ. κάποιο εξειδικευμένο παλμογράφο), την αγορά δημοσιεύσεων ή πατεντών κ.ο.κ. Το κόστος αυτό συγκεντρώνει όλα τα παραπάνω και μόλις αποφασιστεί η μαζική κατασκευή του προϊόντος, τότε μπορεί να υπολογιστεί, ώστε να διευκρινιστεί και η τιμή πώλησης στο ράφι.

Το κόστος μονάδας είναι ένα επαναλαμβανόμενο κόστος και εμπεριέχει όλα τα επιμέρους κόστη για την αγορά των υλικών, την αποστολή στα κατάλληλα εργοστάσια, το τύπωμα των πλακετών, την συναρμολόγηση, τη δοκιμή του κάθε προϊόντος, τη μισθοδοσία όσων ασχολούνται με την κατασκευή (ή σε περίπτωση που έχει γίνει εξωτερική ανάθεση (outsourcing) το κόστος αυτής, το πακετάρισμα και την αποστολή στις κεντρικές αποθήκες. Αυτό το κόστος πληρώνεται κάθε φορά που κατασκευάζεται ένα τέτοιο προϊόν. Το κόστος αυτό μεταβάλλεται κάθε φορά ανάλογα με την ισοτιμία των νομισμάτων (αν κάποια πληρωμή γίνεται σε άλλο νόμισμα, π.χ. σε κινέζικα γουάν), ανάλογα με τον προμηθευτή (μερικές φορές επιλέγονται πιο οικονομικοί προμηθευτές για να μειώσουν το κόστος οι εταιρίες), ή ανάλογα και με την ποσότητα των μονάδων που κατασκευάζονται (άλλο κόστος έχει η κατασκευή 100 πλακετών και άλλο για

, σύμφωνα με την οικονομία κλίμακας).

Αφού υπολογισθούν αυτά τα 2 κόστη η εταιρία αποφασίζει το επιθυμητό περιθώριο κέρδους, έστω . Κάποιες εταιρίες π.χ. αρκετά εξελιγμένων τηλεφώνων που τιμολογούν τα κινητά τους πάνω από 600 ευρώ, έχουν ένα περιθώριο κέρδους περίπου 50%. Ο υπολογισμός της τιμής πώλησης του προϊόντος υπολογίζεται από την εξίσωση:

Για να μειωθεί το κόστος NRE, μια πολύ χρήσιμη τακτική είναι η επαναχρησιμοποίηση αν όχι ολόκληρου του σχεδιασμού, όσο το δυνατόν μεγαλύτερου τμήματος, ώστε το NRE κόστος να διαιρεθεί σε πολλά προϊόντα. Έτσι, είναι πολύ συχνό το φαινόμενο της ίδιας βασικής αρχιτεκτονικής, να επαναχρησιμοποιείται σε πολλά προϊόντα με μόνη διαφορά την προσθήκη 1-2 νέων στοιχείων και τη συγγραφή κατάλληλου κώδικα. Ένα παράδειγμα είναι π.χ. μια επαγωγική κουζίνα χωρίς ώρα και η ίδια επαγωγική κουζίνα με δυνατότητα εμφάνισης της ώρας σε μια οθόνη και χρονοπρογραμματισμό μαγειρέματος (η μόνη διαφορά του βασικού σχεδιασμού με αυτόν, είναι ότι έχει προστεθεί ένα σύστημα RTC με κόστος USD$1, πέντε νέες οθόνες 7-στοιχείων για την εμφάνιση της ώρας, 2-3 κουμπιά και το κατάλληλο λογισμικό· έτσι, το NRE κόστος διαιρείται σε 2 προϊόντα και άρα είναι μικρότερο ανά προϊόν.

Με τον όρο χρόνο εισαγωγής του προϊόντος στην αγορά (time-to-market), εννοούμε το χρονικό διάστημα από τη σύλληψη της ιδέας ως την τοποθέτηση του προϊόντος στο ράφι. Αυτό το χρονικό διάστημα καλύπτει όλες τις φάσεις έρευνας αγοράς, μοντελοποίησης, σχεδιασμού, κατασκευής και θα πρέπει να είναι αρκετά μικρό. Έχει υπολογιστεί ότι για τα ΕΣ θα πρέπει να είναι περίπου 6 μήνες, διαφορετικά υπάρχει σημαντική απώλεια εσόδων.

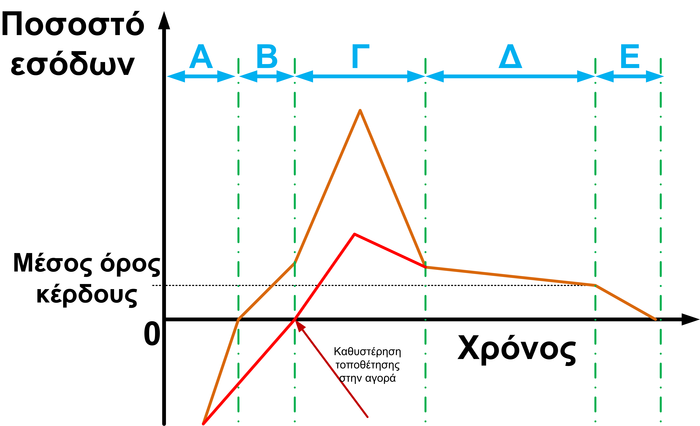

Κάθε προϊόν, έτσι και τα ΕΣ ακολουθούν συγκεκριμένες φάσεις κερδοφορίας. Το Σχήμα 1.13 παρουσιάζει αναλυτικά όλες αυτές της φάσεις. Στον κατακόρυφο άξονα υπάρχει το ποσοστό τον εσόδων και ασφαλώς, όσο πιο μεγάλη είναι αυτή η τιμή τόσο περισσότερα έσοδα έχει η εταιρία, και στον οριζόντιο άξονα βρίσκεται ο χρόνος. Τα έσοδα μπορούν να υπολογιστούν αν υπολογιστεί το εμβαδόν του σχήματος που περικλείεται από την γραμμή του ΕΣ ως τον οριζόντιο άξονα και αφαιρεθεί το εμβαδόν του σχήματος κάτω από τον άξονα. Όσο μεγαλύτερο είναι το εμβαδόν τόσο μεγαλύτερα είναι τα έσοδα.

1.13: Κάθε προϊόν ακολουθεί συγκεκριμένες φάσεις κερδοφορίας. Μια καθυστέρηση τοποθέτησης στην αγορά μειώνει τα κέρδη.

Οι φάσεις που διέρχεται ένα προϊόν είναι πέντε. Μια σωστή τοποθέτηση του προϊόντος ακολουθεί την πορτοκαλί γραμμή (που έχει και τα περισσότερα έσοδα). Στην πρώτη φάση (φάση Α) δεν έχει αναπτυχθεί το προϊόν και έτσι η εταιρία δεν έχει έσοδα παρά μόνο έξοδα. Τα έξοδα αυτά κυρίως είναι τα NRE, αφού βρίσκεται στη φάση της έρευνας και ανάπτυξης. Μόλις τελειώσει αυτή η φάση, το ΕΣ τοποθετείται στα ράφια (φάση Β) και με την κατάλληλη προώθηση υπάρχουν πωλήσεις και άρα έσοδα. Αν σε αυτό το σημείο δεν υπάρχουν έσοδα σημαίνει ότι κανείς δε θέλει αυτό το προϊόν και άρα είχε γίνει λάθος εκτίμηση και πρέπει να τροποποιηθεί κατάλληλα. Στη φάση Β βρίσκονται οι καταναλωτές που ονομάζονται early adopters (πρώιμοι καταναλωτές). Όταν συγκεντρωθεί μια κρίσιμη μάζα από αυτούς τους χρήστες και πουληθεί ένας ικανοποιητικός αριθμός ΕΣ, τότε θα προωθείται αυτόματα μέσα σε φόρουμ συζήτησης και περιοδικά, και έτσι οι πωλήσεις θα εκτοξευθούν (αν είναι ενδιαφέρον και καινοτόμο). Αυτή είναι η φάση Γ. Κάποια στιγμή τα έσοδα θα αρχίσουν να μειώνονται και αυτό γιατί είτε επειδή όσοι χρειάζονταν αυτό το προϊόν το έχουν αγοράσει, είτε επειδή άλλες εταιρίες έχουν αντιγράψει και κλωνοποιήσει και έτσι υπάρχουν και άλλοι προμηθευτές. Σιγά σιγά τα έσοδα δεν θα μειώνονται με τόσο μεγάλο ρυθμό και θα πλησιάζει το μέσο όρο κέρδους των προϊόντων της κατηγορίας. Το ΕΣ θα βρίσκεται ακόμη στα ράφια, αλλά οι πωλήσεις του θα είναι σταθερές (φάση Δ). Κάποια στιγμή θα αποσυρθεί το ΕΣ από την αγορά, γιατί δε θα καλύπτει τις νέες ανάγκες, και η κατασκευάστρια εταιρία δε θα μπορεί να συντηρεί και να λειτουργεί μια γραμμή παραγωγής για ένα παρωχημένο προϊόν. Στη φάση Ε θα γίνει η απόσυρση (ονομάζεται EOL, end-of-life ή τέλος ζωής).

Αν ένα προϊόν καθυστερήσει να εισαχθεί στην αγορά (κόκκινη γραμμή), τότε είναι φανερό ότι τα έσοδα θα είναι αρκετά λιγότερα. Για αυτό θα πρέπει ο χρόνος εισαγωγής του προϊόντος στην αγορά να μη ξεπερνάει τους 6 μήνες, ενώ επίσης η τυπική διάρκεια ζωής είναι 18 μήνες.

Ως τώρα έχει γίνει κατανοητό ότι το οικοσύστημα των ΕΣ δεν είναι ομοιογενές, αφού κυμαίνεται από 8bit επεξεργαστές έως και 32bit, από διάφορες εταιρίες με πλήθος λειτουργικών συστημάτων, ή απλώς εκτέλεση σε ‘γυμνό’ υλικό, με ποικίλες απαιτήσεις. Μπορούμε όμως να σταχυολογήσουμε τα χαρακτηριστικά που συναντώνται σε ΕΣ:

Εκτέλεση μιας λειτουργίας ή αρκετά περιορισμένων σε αριθμό διεργασίες: Όλα τα ΕΣ εκτελούν σε ένα αέναο βρόχο ένα πρόγραμμα που λαμβάνει δεδομένα από αισθητήρια και επιτελεί κάποιες ενέργειες.

Περιορισμένων δυνατοτήτων: τα ΕΣ χρησιμοποιούν πολύ λιγότερους πόρους (π.χ. επεξεργαστικούς ή μνήμης) ως προς τα αντίστοιχα υπολογιστικά συστήματα των επιτραπέζιων υπολογιστών, και αυτό επειδή ο κατασκευαστής ενός ΕΣ γνωρίζει ακριβώς τους πόρους που χρειάζεται η εφαρμογή του και επιλέγει το υλικό που ταιριάζει καλύτερα.

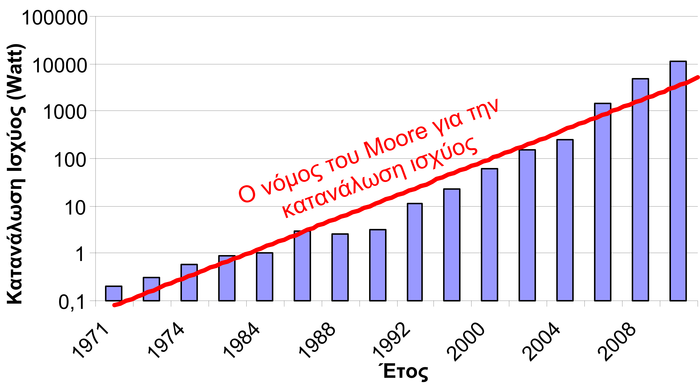

Χαμηλή κατανάλωση ενέργειας και ισχύος: τα φορητά ΕΣ θα πρέπει να έχουν σχεδιαστεί με τέτοιο τρόπο, ώστε να έχουν χαμηλή στιγμιαία κατανάλωση ισχύος, αλλά και χαμηλό κατανάλωση ενέργειας σε μια συγκεκριμένη περίοδο. Αξίζει να σημειώσουμε τη διαφορά μεταξύ της κατανάλωσης ισχύος και της κατανάλωσης ενέργειας. Η κατανάλωση ισχύος αναφέρεται στο έργο που καταναλώνεται στη μονάδα του χρόνου, και στο σύστημα SI μετράται σε Joule / second, γνωστό και ως Watt. Η ενέργεια ομοίως που καταναλώνεται7 σε ένα σύστημα μετράται σε killowatt-hour ή Joules, και αφορά τα watt που έχουν καταναλωθεί σε όλο το χρονικό διάστημα. Για παράδειγμα, ένα ΕΣ που καταναλώνει 1 Watt ισχύ σε 100 ώρες έχει συνολική κατανάλωση ενέργειας 100 watt-hours. Ένα άλλο ΕΣ που καταναλώνει 100 Watt ισχύ σε 1 ώρα, έχει ίδια συνολική κατανάλωση ενέργειας 100 watt-hours. Όμως το προηγούμενο ΕΣ έχει χαμηλότερη κατανάλωση ισχύος, και άρα είναι καλύτερο.

Αντιδραστικά και Πραγματικού Χρόνου: Αρκετά ΕΣ χρησιμοποιούνται σε εφαρμογές που απαιτούν το σεβασμό αυστηρών χρονικών περιορισμών. Για αυτό το λόγο απαιτούνται επεξεργαστές με προβλέψιμο χρόνο εξυπηρέτησης διακοπών και ΛΣ (λειτουργικά συστήματα) που έχουν δημιουργηθεί ειδικά για ανταπόκριση σε πραγματικό χρόνο (RTOS, real time operating systems-λειτουργικά συστήματα πραγματικού χρόνου).

Αξιοπιστία: Τα ΕΣ κατασκευάζονται για να λειτουργούν χωρίς την παρέμβαση κάποιου ανθρώπινου χειριστή, που αν καταρρεύσει το ΛΣ μπορεί να πατήσει το reset και να ξεκινήσει η εκτέλεση από την αρχή. Τα ΕΣ μπορούν να τοποθετηθούν σε πολύ μεγάλα υψόμετρα (π.χ. δορυφόροι) ή σε πολύ χαμηλά (υποβρύχια αισθητήρια), που δε θα υπάρχει κάποιος κοντά. Θα πρέπει λοιπόν να λειτουργούν αξιόπιστα και αδιάκοπτα.

Μικρό κόστος: Το κόστος παραγωγής στα ΕΣ θα πρέπει να είναι ελάχιστο, αφού κατασκευάζονται σε πολύ μεγαλύτερες ποσότητες από ότι τα υπόλοιπα συστήματα. Για αυτό το λόγο στα ΕΣ, οι 8 bit επεξεργαστές καταλαμβάνουν ένα σημαντικό τμήμα της παγκόσμιας αγοράς επεξεργαστών (περίπου 25%), αν και σε όλες τις άλλες περιοχές τα 8bit συστήματα έχουν εξαφανιστεί. Ακόμη και σήμερα κατασκευάζονται και χρησιμοποιούνται ευρέως 8 bit επεξεργαστές που είχαν σχεδιαστεί το 1980 (π.χ. ο Intel 8051), και αυτό επειδή έχουν πολύ χαμηλό κόστος. Γιατί κάποιος να χρησιμοποιήσει 32 bit επεξεργαστή που έχει και μεγαλύτερη κατανάλωση ενέργειας, αν μπορεί να υλοποιήσει τις προδιαγραφές που θέλει με ένα 8 bit;

Μικρό μέγεθος και βάρος: Τα ΕΣ είναι ενσωματωμένα μέσα σε άλλα συστήματα και έτσι πρέπει να καταλαμβάνουν όσο το δυνατόν μικρότερο όγκο. Αυτό σημαίνει και λιγότερο υλικό και άρα πιο περιορισμένους πόρους.

Συνεχή λειτουργία και μεγάλη διάρκεια ζωής: Τα ΕΣ συνήθως από τη στιγμή που θα τεθούν σε λειτουργία θα λειτουργούν αδιάκοπα, και μάλιστα για πάρα πολλά χρόνια. Σε αντίθεση με έναν επιτραπέζιο υπολογιστή που έχει εκτιμώμενο χρόνο ζωής 2 με 4 χρόνια, τα ΕΣ έχουν εκτιμώμενο χρόνο ζωής πάνω από 15 χρόνια που σημαίνει ότι θα πρέπει να έχουν σχεδιαστεί κατάλληλα ώστε να ‘αντέξουν’ και να αντιμετωπίσουν με επιτυχία οποιοδήποτε πρόβλημα προκύψει.

Δυσκολία στην ενημέρωση λογισμικού: Σε αντίθεση με τους τυπικούς υπολογιστές που μπορούν και ενημερώνουν το λογισμικό μέσω διαδικτύου (update), ένα ΕΣ μόλις βγει από το εργοστάσιο δε θα μπορέσει να ανανεωθεί το λογισμικό, κατά μεγάλη πιθανότητα και έτσι δύσκολα θα μπορέσουν να διορθωθούν προβλήματα (κυρίως ασφάλειας) σε διεργασίες που εκτελούνται, και άρα είναι πιο επιρρεπείς στη μη εξουσιοδοτημένη πρόσβαση.

Ασφάλεια: Αρκετά ΕΣ τοποθετούνται σε κρίσιμες υποδομές, όπως π.χ. έλεγχο ενός πυρηνικού αντιδραστήρα. Θα πρέπει να υπάρχει μέριμνα ώστε αυτά τα ΕΣ να προστατεύονται όσο το δυνατόν καλύτερα, αφού αν αποκτήσει κάποιος κακόβουλος χρήστης πρόσβαση σε αυτά θα μπορέσει να τα απενεργοποιήσει ή να τα καταστρέψει. Πραγματικά σενάρια που είδαν το φως της δημοσιότητας αφορούν τη δημιουργία ενός ιού (STUXNET), που κατέστρεψε τα ενσωματωμένα συστήματα στους πυρηνικούς αντιδραστήρες του Ιράν [6], ή τον απομακρυσμένο έλεγχο των ΕΣ ενός οχήματος μέσω δικτύου κινητής τηλεφωνίας από κακόβουλους χρήστες [7].

Κατασκευασιμότητα (manufacturability): Ένα ΕΣ θα πρέπει να κατασκευάζεται σε μεγάλες ποσότητες και για να υπάρχει μειωμένο κόστος θα πρέπει να κατασκευάζεται αυτόματα ή σχεδόν αυτόματα. Με τον όρο κατασκευασιμότητα εννοούμε τις τεχνικές και τα στοιχεία που πρέπει να επιλεχθούν, ώστε να μπορεί εύκολα να κατασκευαστεί σε μεγάλες ποσότητες. Σε αυτό τον όρο συγκαταλέγονται εκτός από το σχεδιασμό της τυπωμένης πλακέτας και του περιβλήματος (housing) και η επιλογή των προϊόντων και των προμηθευτών (ώστε να μπορούν απροβλημάτιστα να παρέχουν τα στοιχεία που απαιτούνται και να μην παρατηρηθεί κάποια έλλειψη, ένα παράδειγμα είναι ότι ο 8051 επεξεργαστής επειδή κατασκευάζεται από πολλές διαφορετικές εταιρίες είναι ένα προϊόν που αποτελεί μια ασφαλή επιλογή για 8bit επεξεργαστή, σε σύγκριση με έναν επεξεργαστή 8bit που κατασκευάζεται από μια μονό εταιρία και μπορεί να χρεοκοπήσει).

Αυξημένη ανάγκη για μείωση του χρόνου εισαγωγής του προϊόντος στην αγορά (time-to-market): Τα ΕΣ προορίζονται κυρίως για καταναλωτικές συσκευές, οπότε θα πρέπει να έχουν ένα πολύ σύντομο χρόνο ολοκλήρωσης. Διαφορετικά, ο κατασκευαστής ενδέχεται να ζημιωθεί, όπως έχει συζητηθεί προηγουμένως.

Όπως φαίνεται από τις παραπάνω προδιαγραφές υπάρχει πολλές φορές σύγκρουση χαρακτηριστικών. Για παράδειγμα η επίτευξη της αξιοπιστίας έρχεται σε σύγκρουση με το μειωμένο χρόνο σχεδίασης. Δικαιολογημένα λοιπόν, ο σχεδιασμός των ενσωματωμένων συστημάτων θεωρείται αρκετά δύσκολος και αγχωτικός με απαίτηση ειδικών γνώσεων από πολλούς τομείς, και για αυτό οι μηχανικοί σχεδιασμού ΕΣ έχουν αρκετά παχυλούς μισθούς [8].

Σε αυτό το κεφάλαιο αναπτύχθηκε η ιστορία των υπολογιστών και έγινε κατανοητό ότι τα σημερινά συστήματα ακολουθούν μια συνεχή εξέλιξη από το 1940 έως σήμερα. Επίσης, δόθηκαν παραδείγματα προδιαγραφών και σχεδίασης ενσωματωμένων συστημάτων, ενώ αφιερώθηκε και ένα τμήμα σε βασικά στοιχεία οικονομίας των ΕΣ. Τέλος, αναφέρθηκαν τα χαρακτηριστικά και οι προκλήσεις των ΕΣ και κατέστη σαφές η δυσκολία σχεδίασης και οι αντικρουόμενες ανάγκες τέτοιων συστημάτων.

Τα επόμενα κεφάλαια διαμορφώνονται ως εξής: Στο κεφάλαιο 2, περιγράφουμε τον τρόπο σχεδιασμού των ΕΣ και την έννοια της μοντελοποίησης. Στο κεφάλαιο 3 αναπτύσσονται τα βασικά στοιχεία που φέρουν τα ΕΣ, όπως η αρχιτεκτονική, η διασωλήνωση, οικογένειες επεξεργαστών, και η κρυφή μνήμη. Στο κεφάλαιο 4 αναφέρουμε τις τεχνολογίες υλοποίησης, θέματα απόδοσης, κατανάλωσης, επαλήθευσης, ενώ στο κεφάλαιο 6 περιγράφουμε πως συνδέονται όλα τα περιφερειακά μεταξύ τους με διαύλους και δίκτυα διασύνδεσης. Σε αυτό το σημείο ολοκληρώνεται το πρώτο μέρος, που αφορούσε το υλικό. Στο δεύτερο μέρος του βιβλίου που αφορά τη βελτιστοποίηση σχεδιασμού πολύπλοκων ενσωματωμένων συστημάτων, περιγράφουμε το πρόβλημα και τη μεθοδολογία επιλογής και χρήσης ενός δυναμικού διαχειριστή μνήμης. Στο πρώτο κεφάλαιο αυτού του μέρους, αναλύουμε τις δυναμικές πολυμεσικές εφαρμογές που εκτελούνται σε ενσωματωμένα συστήματα, στο δεύτερο κεφάλαιο του Β’ μέρους σκιαγραφούμε τα χαρακτηριστικά των δυναμικών εφαρμογών, και στο τελευταίο κεφάλαιο περιγράφουμε με αρκετές λεπτομέρειες τη βελτιστοποίηση της δυναμικής μνήμης για εφαρμογές πολυμέσων.

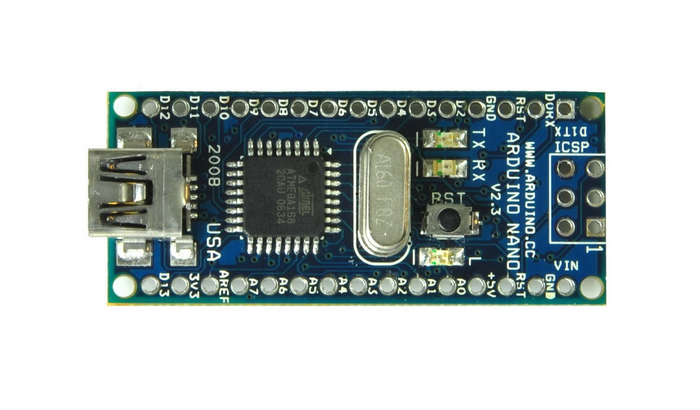

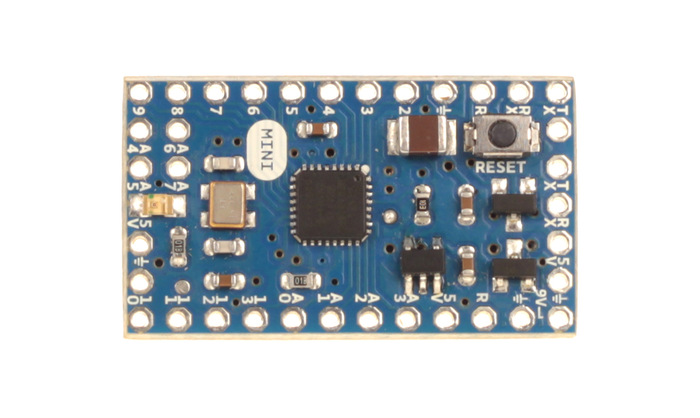

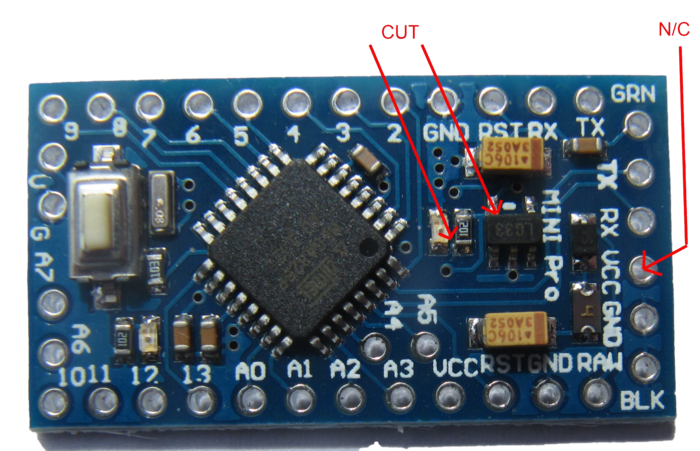

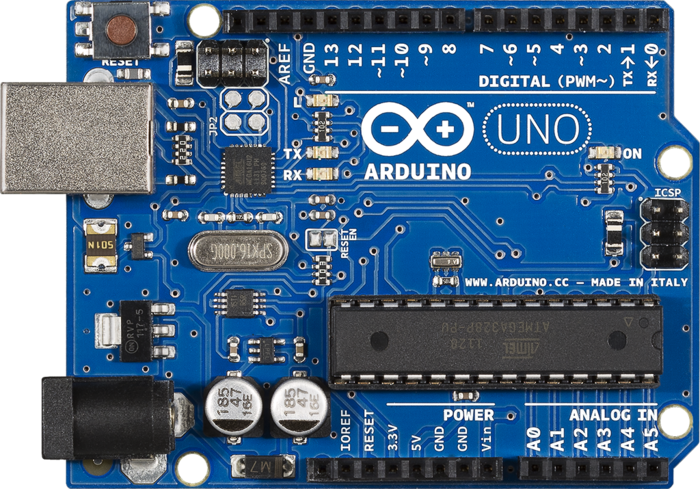

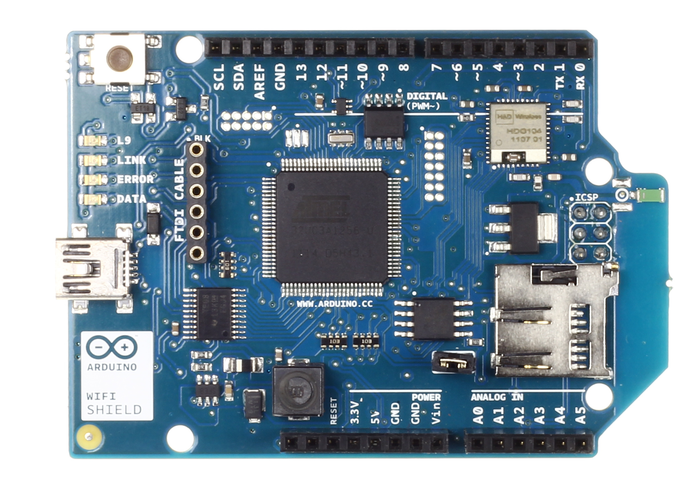

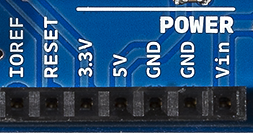

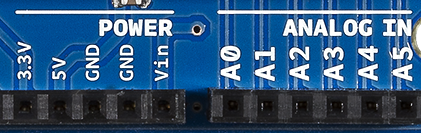

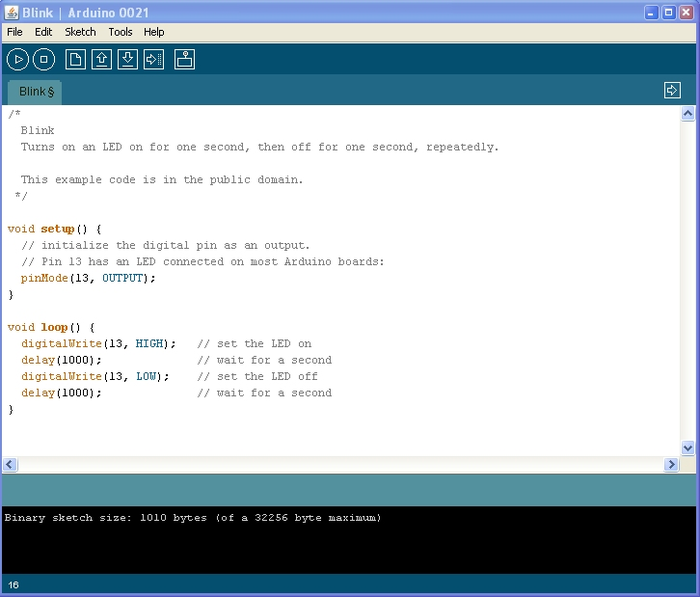

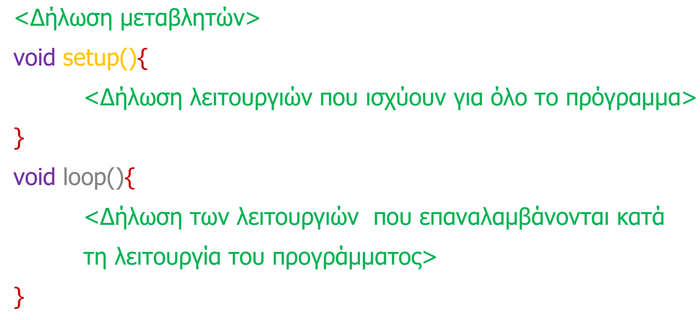

Το βιβλίο αυτό συνοδεύεται από 3 παραρτήματα: Στο πρώτο παράρτημα, υπάρχει μια σειρά εργαστηριακών ασκήσεων για τον 8bit μικροεπεξεργαστή arduino, στο δεύτερο παράρτημα υπάρχουν ασκήσεις βελτιστοποίησης λογισμικού για τον επεξεργαστή ARM, ενώ στο τρίτο παράρτημα υπάρχουν ασκήσεις για τη χρήση επαναδιαμορφώσιμης αρχιτεκτονικής για τις εκπαιδευτικές FPGA πλακέτες Altera DE2-115.

Τέλος, στο βιβλίο αυτό υπάρχει ένας πίνακας των ακρωνυμίων και ένα αναλυτικό λεξιλόγιο μεταφράσεων αγγλικών όρων στα ελληνικά, που έχει δημιουργηθεί από τους συγγραφείς.

O σχεδιασμός ενός ενσωματωμένου συστήματος δεν είναι μια τυποποιημένη διαδικασία που καταλήγει πάντα στην ίδια υλοποίηση. Σπάνια μπορεί να βρεθεί μια βέλτιστη λύση -αν υπάρχει- ως προς κάθε απαίτηση του χρήστη ή του μηχανικού. Αντιθέτως, ο σχεδιαστής πρέπει να λαμβάνει υπόψη του όλες τις απαιτήσεις της εφαρμογής, τα χαρακτηριστικά της διαθέσιμης αρχιτεκτονικής και τους στόχους, και να προτείνει λύσεις που να ικανοποιούν όσο το δυνατόν περισσότερο τις ανάγκες του. Ο σχεδιαστής θα πρέπει διαρκώς να αναλύει και να εκτιμά τους πιθανούς συμβιβασμούς (trade-offs), ενώ ταυτόχρονα θα πρέπει να βελτιστοποιεί όσο το δυνατόν περισσότερο συγκεκριμένα χαρακτηριστικά της εφαρμογής του. Όσον αφορά το σχεδιασμό ενσωματωμένων συστημάτων, ο σχεδιαστής καλείται να μεγιστοποιεί την επίδοση του συστήματος με ταυτόχρονη ελαχιστοποίηση του κόστους. Αυτή η σύγκρουση προκαλεί και την ύπαρξη μιας πληθώρας λύσεων, οι οποίες ικανοποιούν και διαφορετικές ανάγκες. Για παράδειγμα, ένας μηχανικός που θέλει να σχεδιάσει ένα ψηφιακό ρολόι, θα προσπαθήσει να ελαχιστοποιήσει το κόστος και ταυτόχρονα να καλύψει τις ελάχιστες επεξεργαστικές και λειτουργικές απαιτήσεις. Από την άλλη πλευρά, ένας μηχανικός που θα κληθεί να σχεδιάσει έναν ψηφιακό προσωπικό βοηθό (Personal Digital Assistant), θα προσπαθήσει να μεγιστοποιήσει τις επιδόσεις της συσκευής από άλλες παρόμοιες συσκευές, ώστε να έχει καλύτερες επιδόσεις, αλλά με λιγότερη πίεση στο κόστος της συσκευής. Σε όλες λοιπόν τις περιπτώσεις ο στόχος είναι ένας: Μεγιστοποίηση της επίδοσης με όσο το δυνατόν μικρότερο κόστος. Αυτό επιτυγχάνεται με τη μοντελοποίηση.

Η ραγδαία ανάπτυξη των ενσωματωμένων συστημάτων, όπως είδαμε προηγουμένως, δεν οφείλεται μόνο στην πρόοδο που επιτελέστηκε στο υλικό μέρος (π.χ. αύξηση επιδόσεων των επεξεργαστών, αύξηση βαθμού ολοκλήρωσης), αλλά και από το λογισμικό μέρος. Το λογισμικό μέρος είναι αυτό που οργανώνει, κατευθύνει και ελέγχει το υλικό μέρος για τη σωστή και έγκυρη λειτουργία του συστήματος. Όπως τα χαρακτηριστικά του υλικού μέρους επηρεάζουν σημαντικά την ταχύτητα και την κατανάλωση ενέργειας του συστήματος (π.χ. η χρήση ενός πολύ αργού επεξεργαστή θα έχει ως συνέπεια το όλο σύστημα να λειτουργεί με μικρή ταχύτητα), έτσι και το λογισμικό μέρος παίζει έναν κυρίαρχο ρόλο στη διαμόρφωση όλων των μετρικών ενός συστήματος. Ένα λογισμικό μέρος καλά προγραμματισμένο θα βοηθήσει το υλικό μέρος να αποδώσει τα μέγιστα των δυνατοτήτων του, ενώ σε αντίθετη περίπτωση, θα κάνει και το ενσωματωμένο σύστημα με τα πιο γρήγορα υλικά μέρη να μειονεκτεί αισθητά έναντι παρόμοιων συστημάτων.

Το λογισμικό μέρος συμπληρώνει το υλικό μέρος. Η σχέση που συνδέει αυτά τα δύο μέρη είναι παρόμοια (σε ένα αρκετά υψηλό επίπεδο αφαίρεσης), με τη σχέση που έχει ένα όχημα με τον οδηγό του. Αν και το όχημα έχει όλη τη λειτουργικότητα που απαιτείται, εντούτοις περιμένουμε από τον οδηγό να το εκκινήσει, να κάνει τις κατάλληλες ενέργειες, ώστε το όχημα να μετακινηθεί και να οδηγηθεί σε κάποια τοποθεσία που είχε τεθεί ως προορισμός. Μπορεί να θεωρηθεί ότι ο οδηγός παριστάνει το λογισμικό μέρος, ενώ το υλικό μέρος συνδέεται με το όχημα. Έτσι, η συνύπαρξη και των δύο αυτών μερών αποτελεί το συνολικό σύστημα. Παρόλο που και τα δύο είναι αναπόσπαστα μέρη του συστήματος, κατά τα τελευταία χρόνια έχει δοθεί μεγαλύτερη έμφαση στο λογισμικό και, ιδιαίτερα, στους τρόπους καλύτερης μοντελοποίησης και προγραμματισμού των εφαρμογών, ειδικά για ενσωματωμένα συστήματα. Αυτό οφείλεται κυρίως στην τάση που επικρατεί να χρησιμοποιούνται τυπικά εξαρτήματα υλικού μέρους από το ράφι (off-the-shelf components), όπως για παράδειγμα επεξεργαστές των εταιρειών ARM, ή TI, ή μνήμες των εταιρειών Motorola, ή Kingston, κ.τ.λ. Όπως παρατηρείται παγκοσμίως, το πρόβλημα της ανάπτυξης ενός συστήματος, κατευθύνεται περισσότερο προς τη συγγραφή του λογισμικού μέρους, που θα ενεργοποιήσει το υλικό μέρος. Έτσι, η μερική τυποποίηση των υλικών μερών των ενσωματωμένων συστημάτων αποτελεί έναν παράγοντα που έχει μετατοπίσει το πρόβλημα της ανάπτυξης ενσωματωμένων συστημάτων προς το λογισμικό μέρος. Όμως, αυτός δεν είναι ο μόνος λόγος.

Τα τελευταία χρόνια, η ανάπτυξη των εφαρμογών των ενσωματωμένων συστημάτων έχει γίνει ο κυρίαρχος διαμορφωτής του κόστους για έναν ακόμη παράγοντα· αυτός είναι η πολυπλοκότητα των εφαρμογών. Οι πρώτες εκδόσεις των ενσωματωμένων συστημάτων είχαν ένα μικρό πρόγραμμα, το οποίο επιτελούσε κάποιες πολύ απλές λειτουργίες. Μαζί με την απαίτηση της αγοράς για ενσωματωμένα συστήματα με καλύτερες επιδόσεις στο υλικό μέρος, υπήρξε και η απαίτηση για πιο πολλές λειτουργίες, για προγράμματα φιλικά προς το χρήστη, και για εφαρμογές αρκετά απαιτητικές (όπως π.χ. η αναπαραγωγή πολυμέσων). Γι’ αυτόν το λόγο υπήρξε και υπάρχει αρκετά μεγαλύτερη έμφαση στην ανάπτυξη των εφαρμογών ενσωματωμένων συστημάτων.

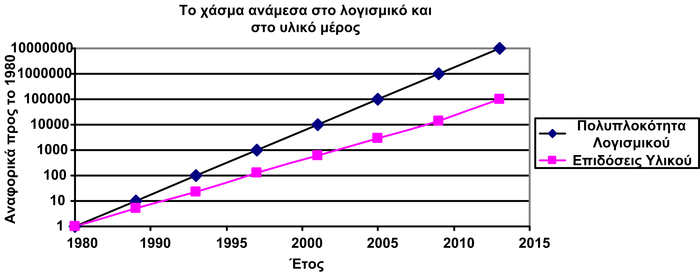

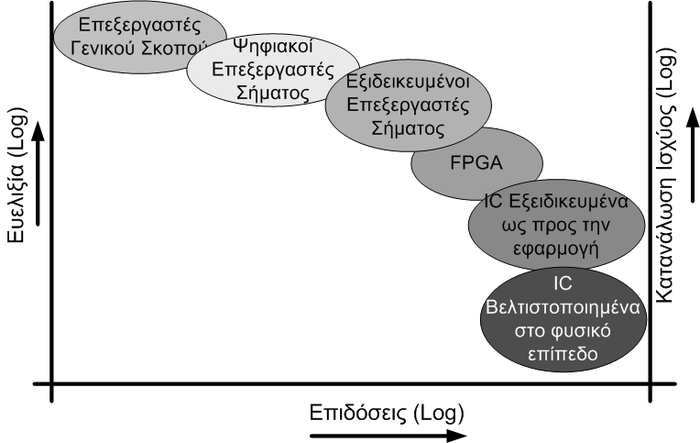

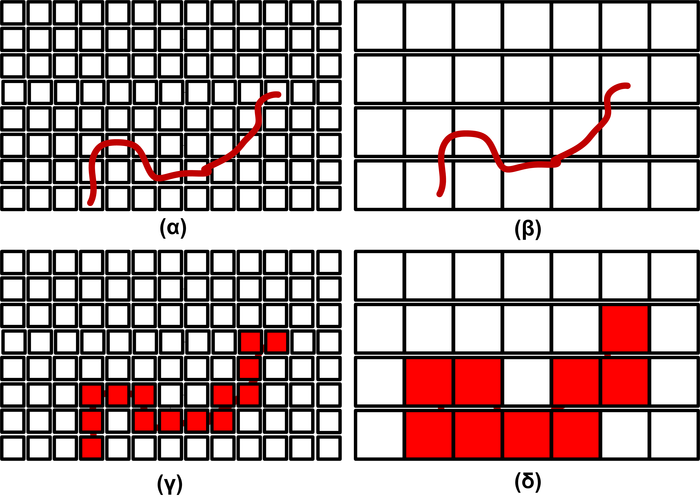

Ένας τρόπος μέτρησης της ανάπτυξης των εφαρμογών αποτελεί και το μέτρο της πολυπλοκότητας των εφαρμογών. Η πολυπλοκότητα μιας εφαρμογής εξαρτάται από τον αριθμό των εντολών και συναρτήσεων που την αποτελούν, από τις λειτουργίες που αυτή κάνει, από το μέγεθος κώδικα που αποθηκεύεται στη μνήμη εντολών, και από τον αποθηκευτικό όγκο σε μνήμη δεδομένων. Αν βγάλουμε χονδρικά ένα μέσο όρο της πολυπλοκότητας των εφαρμογών θα παρατηρήσουμε ότι ακολουθεί μια εκθετική αύξηση χρονολογικά (Σχήμα 2.1). Αν στο ίδιο γράφημα τοποθετήσουμε και τις επιδόσεις των επεξεργαστών, θα δούμε ότι αυτές υστερούν, και δεν μπορούν να καλύψουν τις τρέχουσες απαιτήσεις των εφαρμογών. Βλέπουμε, λοιπόν, ότι υπάρχει ένα χάσμα ανάμεσα στο τι μπορεί να εκτελεστεί σε ένα σύστημα (επιδόσεις υλικού μέρους) και στο τι απαιτούν οι εφαρμογές για να εκτελεστούν (πολυπλοκότητα λογισμικού μέρους).

2.1: Η πολυπλοκότητα των εφαρμογών ενσωματωμένων συστημάτων αυξάνεται με πολύ μεγαλύτερο ρυθμό σε σχέση με τις επιδόσεις των επεξεργαστών.

Το πρόβλημα της δημιουργίας λογισμικού ενσωματωμένων συστημάτων είναι τόσο σημαντικό, ώστε μεγάλες εταιρείες, όπως η Microsoft και η Sun (εταιρείες που έχουν κυριαρχήσει στο λογισμικό μέρος των επιτραπέζιων συστημάτων, ή των διακομιστών), έχουν κατευθύνει μέρος του προϋπολογισμού τους στην έρευνα και ανάπτυξη εφαρμογών ενσωματωμένων συστημάτων. Για παράδειγμα, η Microsoft αναπτύσσει τα Windows Mobile, η Google to Android, και η Sun τη Java Virtual Machine, που όλα συμβάλλουν στην ανάπτυξη λογισμικού ενσωματωμένων συστημάτων.

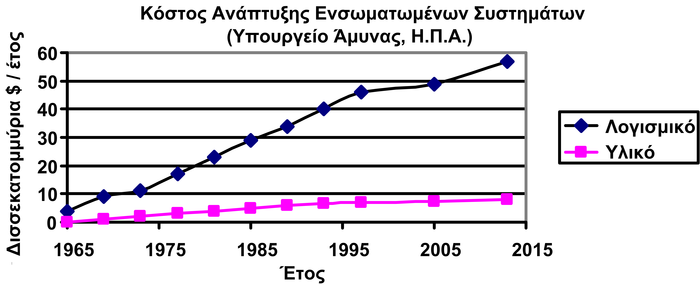

Το λογισμικό μέρος των ενσωματωμένων συστημάτων, είναι ένας ακμάζων τομέας, και αυτό φαίνεται στα οικονομικά μεγέθη που το συνοδεύουν. Για παράδειγμα, τα στοιχεία από το Υπουργείο Άμυνας των Η.Π.Α. – ένας από τους μεγαλύτερους παγκοσμίως αγοραστές ενσωματωμένων συστημάτων – (Σχήμα 2.2), δείχνουν ότι το κόστος ανάπτυξης του λογισμικού είναι έως και 6 φορές μεγαλύτερο από το κόστος ανάπτυξης των υλικών μερών. Είναι γνωστό, ότι το λογισμικό καταλαμβάνει περισσότερο από το 70% του κόστους ανάπτυξης πολύπλοκων ενσωματωμένων συστημάτων, όπως φορητά τερματικά, ηλεκτρονικά συστήματα αυτοκινήτων, συστήματα επικοινωνιών κτλ [9], [10], [11], [12].

2.2: Το λογισμικό μέρος κυριαρχεί στη διαμόρφωση του κόστους ενός ενσωματωμένου συστήματος.

Τέλος, η σπουδαιότητα του λογισμικού των ενσωματωμένων συστημάτων φαίνεται καθαρά και από τα στοιχεία που αναφέρονται στην έκθεση του Υπουργείου Εμπορίου και Βιομηχανίας της Ολλανδίας, στην οποία αναφέρεται ότι ο αριθμός των ατόμων ή εταιρειών που παίρνουν συμβόλαια για ανάπτυξη κώδικα ενσωματωμένων συστημάτων θα αυξηθεί από 2 εκατομμύρια το 1994 σε 13 εκατομμύρια το 2015, ενώ ο αριθμός των κατασκευαστών υλικού ενσωματωμένων συστημάτων θα αυξηθεί από 0,6 εκατομμύρια σε 1,1 εκατομμύρια, αντιστοίχως [13].

Είναι σημαντικό λοιπόν να αναλύεται η εφαρμογή, που θα εκτελεστεί στο ενσωματωμένο σύστημα, και να γίνεται συσχεδιασμός του υλικού και του λογισμικού μέρους. Η μεθοδολογία, σχεδιασμού ΕΣ αποτελείται από στάδια που βελτιώνουν το λογισμικό μέρος και από στάδια που βελτιώνουν το υλικό μέρος. Επίσης, μια σωστή μεθοδολογία έχει εφαρμοστεί με επιτυχία σε ένα πλήθος εφαρμογών, που εκτελούνται σε ενσωματωμένα συστήματα, γεγονός που δείχνει τη γενική χρήση που μπορεί αυτή να έχει.

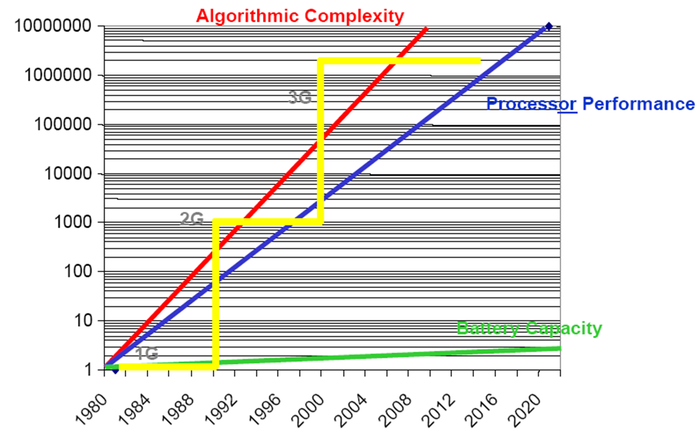

2.3: Η πολυπλοκότητα των εφαρμογών αυξάνεται λογαριθμικά.

Όπως έχει αναφερθεί στην εισαγωγή του βιβλίου, το κόστος έρευνας και ανάπτυξης (non recurrent engineering cost, NRE) ενός ενσωματωμένου συστήματος είναι αποφασιστικής σημασίας για τη διαμόρφωση της τιμής του τελικού προϊόντος, αφού θα πρέπει να ενσωματωθεί στην τελική τιμή. Όσο μεγαλύτερο είναι αυτό το αρχικό κόστος, τόσο πιο πολύ θα αυξηθεί η τιμή των τελικών προϊόντων και ενδεχομένως θα επηρεάσει αρνητικά τον αριθμό πωλήσεων, προκαλώντας ίσως και ζημιά στην εταιρία που το προμηθεύει στην αγορά.

Η μείωση του κόστος NRE είναι λοιπόν ζωτικής σημασίας, αφού η ίδια η βιωσιμότητα μιας εταιρίας εξαρτάται από αυτό, και θα πρέπει να είναι όσο το δυνατόν μικρότερο. Το ίδιο προϊόν μπορεί σε δυο διαφορετικές εταιρίες να συνδέονται με NRE κόστη που έχουν πολύ μεγάλη διαφορά. Το κόστος NRE για το ίδιο προϊόν σε δυο διαφορετικές εταιρίες είναι διαφορετικό. Για να ελαχιστοποιηθεί αυτό το κόστος θα πρέπει να θυμηθούμε (1ο κεφάλαιο) τους παράγοντες που το διαμορφώνουν. Ο πρώτος παράγοντας είναι το κόστος μισθοδοσίας του προσωπικού. Μια εταιρία μπορεί να έχει υψηλό μισθολογικό κόστος λόγω νοοτροπίας ή φορολογίας και ασφαλιστικού, ενώ μια εταιρία σε άλλη περιοχή του πλανήτη μπορεί να έχει υποπολλαπλάσιο κόστος. Για αυτό αρκετές εταιρίες του Δυτικού Κόσμου, προβαίνουν σε εξωτερικές αναθέσεις (outsourcing) ή ανοίγουν παραρτήματα σε χώρες με χαμηλό μισθολογικό κόστος, όπως η Ινδία ή η Κίνα. Ο επόμενος παράγοντας είναι τα πάγια έξοδα των κτιρίων. Ομοίως, αυτό μπορεί να μειωθεί σε μετεγκατάσταση της εταιρίας είτε σε κατάλληλη οικοδομική ζώνη που παρέχει σε μικρότερο κόστος κτιριακή επιφάνεια, νερό, ρεύμα και διαδίκτυο, ή σε μετεγκατάσταση σε άλλη πόλη ή χώρα. Ένας άλλος παράγοντας, είναι το κόστος των υλικών για τη δημιουργία του πρωτοτύπου. Αν και αυτό το κόστος είναι συνήθως μικρότερο από τα δυο προηγούμενα, εντούτοις διαμορφώνει και αυτό το NRE, ιδιαίτερα αν πρέπει να γίνουν πολλά και μακροχρόνια πειράματα, δοκιμάζοντας πολλά διαφορετικά σενάρια ή σχεδιασμούς. Για να μειωθεί αυτό το κόστος, εκτός από την προμήθεια των υλικών από πάροχο που έχει τις χαμηλότερες τιμές και ταυτόχρονα καλύπτει τα επίπεδα αξιοπιστίας, ποιότητας και ταχύτητας παράδοσης, θα πρέπει να ακολουθηθεί μια τεχνική που θα επιτύχει μείωση του χρόνου, μείωση των λανθασμένων σχεδιαστικών επιλογών και μείωση των προβληματικών πρωτοτύπων. Αυτή η τεχνική ονομάζεται μοντελοποίηση, και είναι πάντα το πρώτο βήμα σε οποιαδήποτε μεθοδολογία σχεδιασμού, είτε ενσωματωμένων συστημάτων είτε οποιοδήποτε άλλου προϊόντος.

Η μοντελοποίηση είναι μια τεχνική (ή για να είμαστε ακριβείς, ένα σύνολο από τεχνικές) που επιτρέπουν ένα σχεδιαστή να πετύχει το στόχο του με την πρώτη προσπάθεια. Αν και έχει μεγάλη σημασία, αρκετές φορές παραλείπεται από τα επίσημα διαγράμματα σχεδίασης, λόγω χρονικής πίεσης, αφού κάποιοι σχεδιαστές πιστεύουν ότι μπορεί να καταφέρουν το τελικό αποτέλεσμα (π.χ. την ανάπτυξη ενός ΕΣ) με τη σύνδεση των δομοστοιχείων και τη συγγραφή του κώδικα. Αν και μπορεί να το πετύχουν και να σχεδιάσουν κάτι που να λειτουργεί, εντούτοις η μεγαλύτερη πιθανότητα είναι ότι δε θα το καταφέρουν και θα χάσουν το παράθυρο εισαγωγής στην αγορά, με δυσάρεστες οικονομικές συνέπειες. Αλλά, ακόμη και να τα καταφέρουν, δε σημαίνει ότι το τελικό αποτέλεσμα θα είναι στιβαρό και θα λειτουργεί σε οποιαδήποτε συνθήκη.

Παραδείγματα που δείχνουν τη σημασία της μοντελοποίησης μπορούμε να βρούμε σε κάθε χώρο. Ένα προσωπικό απλό παράδειγμα του συγγραφέα κατά την επίβλεψη μιας εργασίας φοιτητή, ήταν όταν έπρεπε να δημιουργηθεί μια συσκευή συνδεδεμένη στο Internet που έλεγχε τέσσερα ρελέ. Ο σχεδιασμός έγινε χωρίς μοντελοποίηση και εξέταση των αναγκών από το φοιτητή. Το πρωτότυπο συνδέθηκε στην τροφοδοσία και λειτούργησε με επιτυχία για 1 συσκευή. Όταν όμως συνδέθηκε και δεύτερη συσκευή, τότε παρουσιάστηκε δυσλειτουργία με τυχαία συμπεριφορά. Το πρόβλημα ήταν ότι δεν είχε μοντελοποιηθεί η ζητούμενη απαίτηση ρεύματος σε πλήρη λειτουργία (και με τα 4 ρελέ), οπότε το τροφοδοτικό των 300 mA, ενώ επαρκούσε για τον έλεγχο ενός ρελέ, δεν επαρκούσε για την ικανοποίηση της χειρότερης κατάστασης. Ένα άλλο παράδειγμα, αφορά το σχεδιασμό ενός ιστοχώρου εξέτασης φοιτητών, όπου ενώ λειτουργούσε σωστά όταν ήταν συνδεδεμένοι 1-2 φοιτητές, σε περίπτωση που συνδέονταν και οι 100 φοιτητές, δε λειτουργούσε καθόλου επειδή ο φόρτος του διακομιστή από 1% γίνονται 3000%. Το πρόβλημα ήταν στον αριθμό των ερωτημάτων ανά σελίδα που ήταν υπερβολικά πολλά, επειδή δεν είχε μοντελοποιηθεί πως να κλιμακώνεται. Με τη βελτίωση της σελίδας και τη μείωση των ερωτημάτων, το σύστημα μπόρεσε και λειτούργησε. Σε αυτά τα παραδείγματα φάνηκε ότι ακόμη και να λειτουργεί, αν δεν έχει προηγηθεί μια ανάλυση και μοντελοποίηση, τότε μπορεί να υπάρξουν περιπτώσεις που θα αποτύχει ή απαιτείται επιπρόσθετος χρόνος σχεδίασης για να βρεθεί το πρόβλημα στο τελικό προϊόν και να διορθωθεί. Ακόμα, αν αυτό το προϊόν κατασκευαστεί και διατεθεί, και αποτύχει σε μια κρίσιμη στιγμή, μπορεί να υπάρξει και απώλεια υλικής αξίας ή ανθρώπινης ζωής.

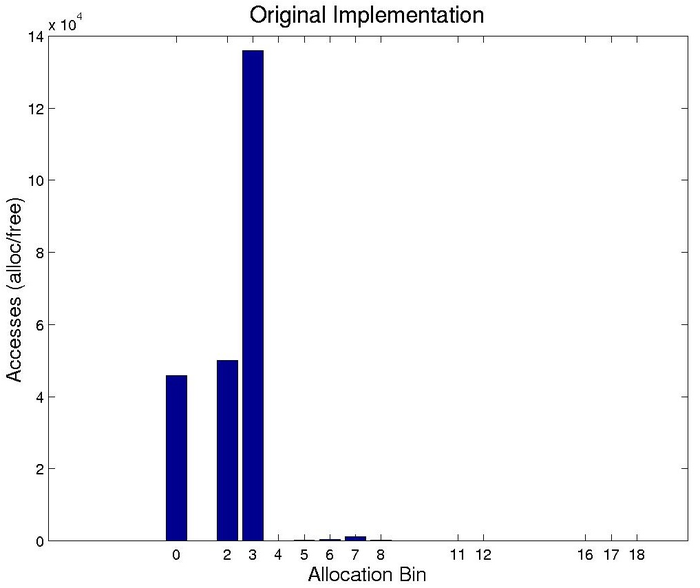

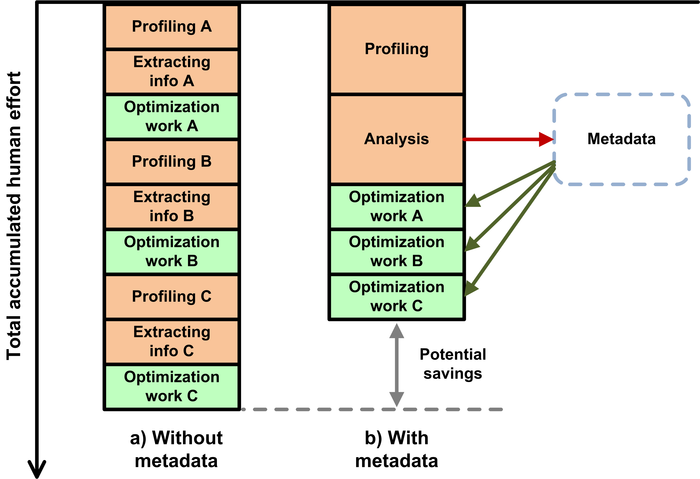

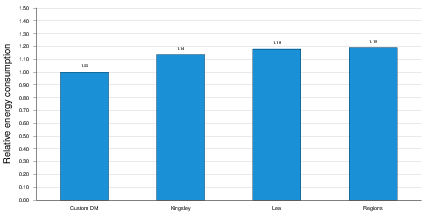

Η μοντελοποίηση δεν ανήκει στα βήματα της μεθοδολογίας που θα ήταν καλό να γίνουν (‘nice to do’). Ανήκουν στα βήματα που πρέπει να γίνουν (‘must do’). Η σημαντικότητα αυξάνεται όσο περισσότερο αυξάνονται η πολυπλοκότητα και οι απαιτήσεις. Αν κάποιοι αποφασίσουν να κατασκευάσουν μια αποθήκη με ξύλα, αρκεί να σημειώσουν σε ένα χαρτί τις διαστάσεις των τοίχων, τα εργαλεία και τα υλικά που θα χρησιμοποιήσουν. Σε περίπτωση που δεν ταιριάζουν κάποια υλικά μεταξύ τους μπορεί να γίνουν κάποια μπαλώματα για να τα καλύψουν. Αν όμως απαιτείται η κατασκευή ενός σπιτιού με πολλούς χώρους, τότε αυξάνεται η πολυπλοκότητα και θα πρέπει να ληφθούν υπόψιν πολλά περισσότερα στοιχεία, όπως διελεύσεις των καλωδίων, των δικτύων ύδρευσης και αποχέτευσης, τα πάχη των τοίχων μαζί με τη μόνωση, τα κουφώματα και πλήθος άλλων λεπτομερειών. Αν δε γίνει αυτό, στο τέλος μπορεί να μην καλύπτονται οι προδιαγραφές κατοίκησης και να μην έχει σωστή μόνωση ή μπορεί να ξεχάσουν να βάλουν βρύσες στο μπάνιο ή ακόμη αν είναι πολυκατοικία να υπάρχει κατάρρευσή, αν δεν έχει γίνει μοντελοποίηση των στατικών φορτίων. Για αυτό είναι απαραίτητο να μοντελοποιηθεί η κατασκευή ενός τέτοιου σύνθετου σχεδιασμού και μάλιστα, όχι μόνο με μια κάτοψη. Θα πρέπει να γίνει μια θερμική μελέτη, ηλεκτρολογική μελέτη, μελέτη ύδρευσης και αποχέτευσης, στατική μελέτη και άλλα. Σε περίπτωση που υπάρξει πρόβλημα σε μια τέτοια κατασκευή μπορεί να είναι δύσκολο να διορθωθεί, με αποτέλεσμα να υπάρχει σημαντική οικονομική καταστροφή.